采用超薄ITO界面层在N极性面上获得低接触电阻率的垂直氮化镓肖特基势垒二极管

2023/7/28 16:35:26 材料来源:雅时

深圳大学:刘新科, 王灏帆,吴钧烨,邹苹,陈少军,熊信柏,钟泽

深圳大学微纳光电子研究所:屠宇迪

深圳信息技术研究所:王新中

东莞中镓半导体有限公司:韩甲俊,庄文荣

东莞南方半导体技术有限公司:杨志超

晶瑞(深圳)科技创新中心有限公司:邱峰

台湾长庚大学:邱显钦

摘要-本文首次研究了一种基于氧化铟锡(ITO)/Ti/Al/Ni/Au的高性能氮化镓肖特基势垒二极管(SBD)的欧姆接触结构。由于超薄的氧化铟锡(ITO)界面层,可以减轻金属-半导体接触界面中的费米钉扎(FLP)效应,在相同的测试条件下,N极性面上的比接触电阻率(ρc)从3.32×10-3降低到7.36×10-5 Ω·cm2,器件的导通电阻(RON,sp)从3.14降低到1.17 mΩ·cm2。采用氦离子注入技术,实现了高击穿电压VBR为1100 V,低开启电压VON为0.63 V,品质因子(VBR2/RON,sp)为1.04 GW/cm2。本研究中制备的带有ITO界面层的垂直GaN SBD在报道的具有指定阳极尺寸的GaN-GaN SBD中达到了最低的ρc。

关键词:GaN-GaN,垂直SBD,氧化铟锡,界面层,欧姆接触,N极性面。

1.引言

GaN因其宽带隙、高击穿电压、高热导热率、高电子饱和速度和电子迁移率而被广泛应用于射频和功率电子器件。随着GaN材料生长技术不断发展,GaN器件性能也在不断提高。

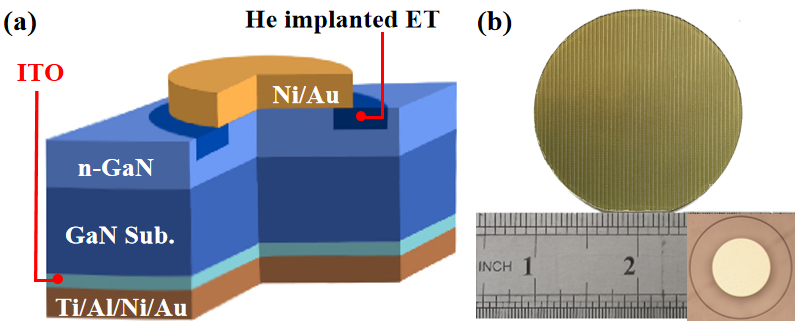

图1(a) ITO界面层欧姆接触的垂直GaN SBD的三维示意图。(b)制备的器件在2英寸独立(FS)-GaN晶片上的光学图像。

在电力电子设备中,垂直GaN SBD由于低晶格失配和热膨胀失配、表面缺陷密度较低、器件面积较小而受到越来越多的关注。对于垂直功率二极管,高击穿电压(VBR)和低电阻(RON,sp)是必不可少的。目前,已经提出了几种提高垂直GaN SBD VBR的方法,如场板、等离子体处理、离子注入终端(ET)和保护环。虽然VBR已经达到了一个较高的水平,但由于其RON,sp值较高,仍没有达到GaN材料的理论极限。与Ga极性面n-GaN相比,由于其不同的表面性质,N极性面上的欧姆接触更难实现低ρc。N极性面GaN有着更为复杂的表面态,这也将导致更高的肖特基势垒高度(SBH),同时也使电极的制备成为挑战。目前已经提出了几种方法来优化垂直GaN器件的欧姆接触,如等离子体处理去除表面氧化物,减少氮空位(VN),得到约3×10-4 Ω·cm2的比接触电阻率(ρc),用功函数低的金属TiN取代Ti接触层,达到6×10-4 Ω·cm2的ρc;通过激光辅助掺杂引入重掺杂区,使ρc降至8.72×10-5 Ω·cm2。然而,这些方法并没有很好地在垂直GaN SBD上得到很好地实现,RON,sp也没有得到有效降低。

在本研究中,我们首次在GaN和Ti/Al/Ni/Au之间植入超薄的氧化铟锡(ITO)界面层,制备了一种性能优良的器件。这种结构很可能直接屏蔽金属波函数直接隧穿进入半导体,有效地减轻费米能级钉扎(FLP)效应。最后,在N极性面上实现了高质量的欧姆接触,并降低了RON,sp。同时,通过引入He离子注入终端结构来改善VBR,我们在目前已报道的GaN SBD中实现了最低的ρc,为7.36×10-5 Ω·cm2。

2.器件制备

图1(a)为在形成欧姆接触时,具有ITO界面层的垂直GaN-on-GaN SBD的结构示意图。图1(b)显示了2英寸独立(FS)晶片上的光学图像。它由掺杂Si的300 μm厚GaN衬底和轻掺杂的20 μm漂移层组成,掺杂浓度为2×1016 cm-3(SINO Nitride, China)。

首先,晶圆经过预清洗过程,过程包括5分钟丙酮、5分钟异丙醇脱脂步骤和10分钟食人鱼溶液(H2O2:H2SO4 = 1:3)浸渍步骤,以去除有机残留物。然后,用MOCVD法在清洗后的衬底上生长n-GaN漂移层。用BCl3/Cl2等离子体蚀刻了深度为1 μm的台阶结构作为隔离区和标记区域。然后在室温下注入He离子,浓度为1×1015 cm-2,入射角为7°,注入能量分别为150 keV和50 keV,最终形成0.8 μm深的箱状轮廓。随后采用圆形传输线模型(CTLM)测量了欧姆接触点的比接触电阻率。CTLM法内径和外径间隙间隔分别为(15、20、30、40、50、60 μm),内径固定在200 μm,采用光刻技术(SUSS-MA6)形成图案。然后,用磁控溅射法沉积了ITO界面层。ITO溅射参数为衬底温度25 ℃,55 sccm 的Ar2氛围,等离子体功率为70 W。步长测量表明,沉积的ITO界面层厚度为10 Å。样品在540℃下通过快速热退火(RTA)退火5 min。此外,用真空蒸镀仪(ASB-EPIC6)在ITO界面层上沉积金属Ti/Al/Ni/Au(25 nm/100 nm/20 nm/60 nm),然后在800℃、N2氛围下退火60 s。

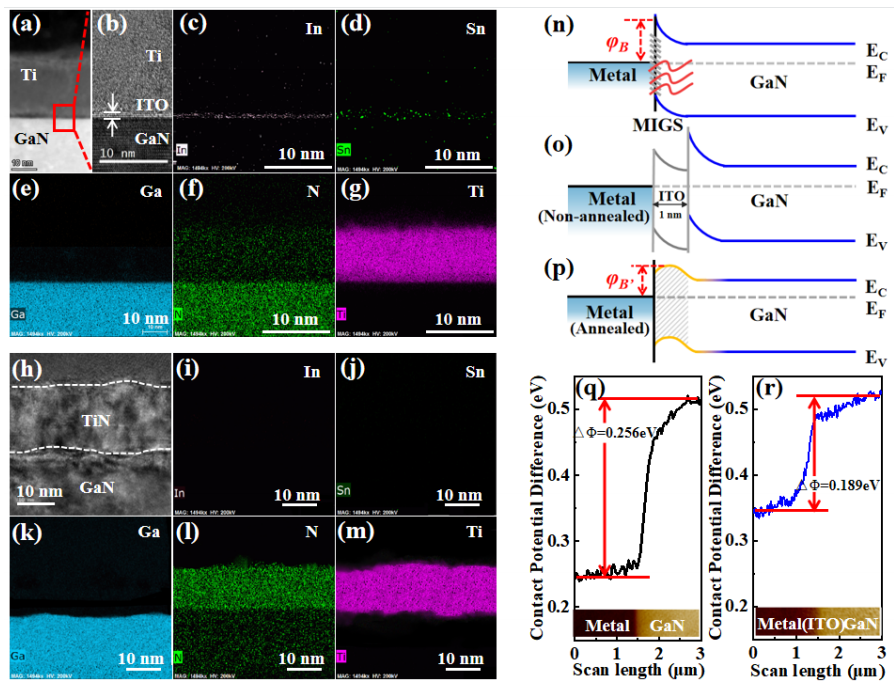

图2(a)-(g)退火前在ITO界面层区域拍摄了高分辨率的TEM图像和每个元素的EDS映射信号,以及退火后的图像(h)-(m)。(n)在半导体和金属之间由MIGS引起的费米能级钉扎引起的肖特基势垒形成的能带图 。(o)退火前与ITO界面层的能带图。 (p)退火后的ITO能带图。基于开尔文法,(q)在有ITO的器件和(r)无ITO的器件的情况下测量电位差。

最后,沉积直径100 μm的Ni/Au(20/100 nm)形成阳极。同时,我们制作了不含ITO界面层的垂直GaN器件进行比较。

3.结果与讨论

如图2(a)-(g)所示,退火前ITO界面层和铟(In)、锡(Sn)、镓(Ga)、氮(N)、钛(Ti)的EDS映射信号,Ti层与氮化镓之间可见均匀的1 nm厚的ITO界面层。经过800℃退火后,N原子扩散到Ti层中,形成TiN层,如图2(h)、2(i)和2(m) 所示。同时,金属In和Sn的高温扩散耗尽了ITO层,因此不能作为界面层被清晰地观察到。In和Sn,可能扩散进入金属/GaN层,且ITO界面层在退火后以自我牺牲的方式修复半导体与金属之间的界面,进一步减轻了费米能级钉扎效应。能带图如图2(n)所示,可以看作是金属诱导的间隙态(MIGs),金属波函数直接渗透到半导体中,增强了FLP效应,增加了SBH。相比之下,ITO扩散到金属/GaN层中可以有效地避免波函数的穿透。如图2(o)和2(p)所示,退火后的ITO扩散到金属/GaN中,修复了界面,使FLP效应减轻,界面之间的SBH值降低。用开尔文探针力显微镜(KPFM)测量开尔文探针和样品之间的电位差,见图2(q)和2(r)。当两种具有不同功函数的金属相互接触时,电子将从功函数较低一侧传输到功函数较高的一侧,从而使它们的费米能级再次对齐,因此产生了接触电位差。当在两个金属板之间施加直流补偿电压VDC时,可以通过调整VDC使VDC = VCPD。如果已知一个金属板的功函数为Φ1,则另一金属板的功函数可以表示为Φ2 = Φ1 - eVCPD,因此可以计算出SBH分别为△Φ = 0.256 eV和△Φ = 0.189 eV。可见,含ITO的样品的SBH比不含ITO的样品低0.067 eV。这可能是由于退火后在电极的界面上形成了一层功函数较低的物质。引入纳米级ITO自牺牲层缓解费米能级钉扎效应,使GaN与金属电极之间的欧姆接触特性可以被金属的功函数调制,功函数较低的金属可以降低有效SBH,从而在n-GaN上建立更好的欧姆接触。

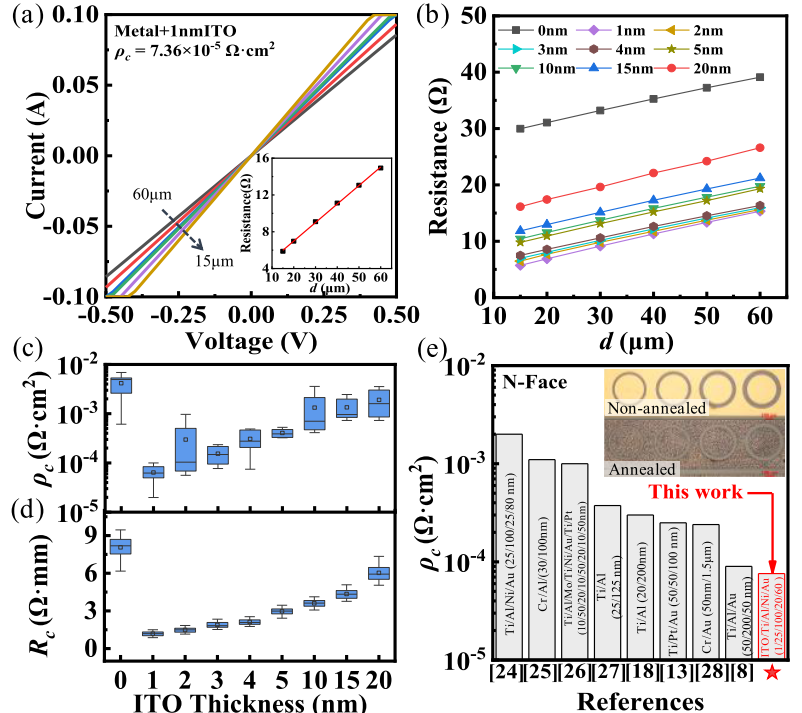

图3(a)显示了具有1 nm ITO界面层的N极性面GaN上的欧姆接触点的I-V特性和相应的接触电阻率。

图3(a)用CTLM法在1 nm ITO/Ti/Al/Ni/Au接触N极性面GaN的I-V特性,插入图显示了RT和间隙间距的拟合线图。(b)通过CTLM测试了不同厚度的ITO界面层的RT和间隙间距的拟合线性图。(c)最低可达到的ρc和(d) Rc随ITO厚度的不同而变化,每种条件下至少测量了8个样品。(e)对N面欧姆接触的结构和比接触电阻率的调研,插图显示了退火前(顶部)和退火后(底部)的CTLM光学图像。

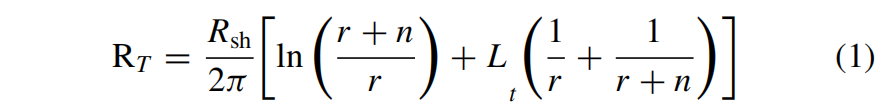

I-V曲线的斜率随着间隙间距的增加而减小,插图显示了环间距与总电阻(RT)之间的拟合线形图。图3(b)为通过CTLM测试的不同厚度ITO界面层的RT和间隙间距的拟合线性图,其中拟合线的斜率为方块电阻(Rsh),截距为接触电阻(Rc)。其中,CTLM的相关参数可以通过以下公式提取:

其中,Rsh是金属电极与半导体材料接触之间的方块电阻;Lt是传输线长度。r为内径,n为间隙间距。然后,拟合RT为纵坐标, 为横坐标,得到的拟合线的截距为Rc,斜率为Rsh,由下式可以得到ρc:

为横坐标,得到的拟合线的截距为Rc,斜率为Rsh,由下式可以得到ρc:

![]()

从图中可以看出,随着ITO厚度的逐渐减小,拟合截距也逐渐减小,说明相应的接触电阻也在减小。拟合线的线性度表明了所制备器件的稳定性良好。为了进行比较,每种条件下至少测试了8个样品,可以发现在溅射1 nm的ITO界面层后,得到了最佳的欧姆接触性能。ITO层各厚度的退火温度为800 ℃,温度选择是基于实验数据。退火前后见图3(e)插入的光学图像,顶部为未退火CTLM样品图像,底部为800 ℃退火后图像。

图3(c)和(d)中,1 nm的最低Rc ~ 1.22 Ω·mm,ρc ~ 7.36×10-5 Ω·cm2。图3(e)主要显示了近年来对N极性面欧姆接触的这种结构和比接触电阻率的研究。这也反映了在本工作中制备的欧姆接触的巨大潜力。两种器件的开启电压(VON)如图4(a)中均为0.63 V,表明ITO界面层对SBD器件的开启性能没有副作用。此外,我们还发现,在低电流水平下,电流的主要传导机制是热电子发射(TE)。基于TE模型,SBD的正J-V性质描述如下公式:

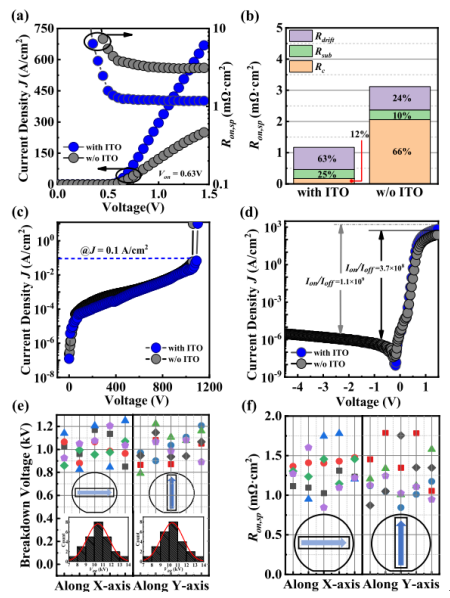

图 4(a)两种器件的正向 J-V 特性和 RON,sp图。(b)每个器件导通电阻及其组成部分。(c)分别给出了有和没有ITO界面层的垂直GaN二极管的反向J-V特性。(d)两种器件的J-V开关比。(e)具有ITO界面层的器件在2英寸晶圆上沿X轴和Y轴的25点的击穿电压,插图显示BV的正态分布趋势。(f)具有ITO界面层的器件在2英寸晶圆上沿X轴和Y轴25点的特定导通电阻。

式中,J为饱和电流密度,A*为理查森常数(26.4 A·cm-2·K-2),T为绝对温度,q为电子电荷,ΦB为势垒高度,V为正向偏置电压,k为玻尔兹曼常数,n为理想因子。有ITO界面层和无ITO界面层的样品的RON,sp分别为1.17 mΩ·cm2和3.12 mΩ·cm2。如图4(b)所示,RON,sp主要可分为以下三部分公式:

![]()

其中Rsub是衬底的电阻,Rdrift是轻掺杂漂移层的电阻,Rc是接触电阻。漂移层可以用以下公式来估计:

其中,t、μ和Nd分别为厚度、载流子迁移率和净载流子浓度。基于掺杂浓度(~2×16 cm−3)和载流子迁移率(850 cm2·V−1·s−1),和衬底电阻率(~0.01 Ω·cm),理论上,有ITO界面层的器件Rdrift和Rsub分别计算为0.71 mΩ·cm2和0.29 mΩ·cm2。根据ρc ~ 7.36×10-5 Ω·cm2,Rc可为0.17 mΩ·cm2。因此,Rdrift、Rsub和Rc分别占总RON,sp的~63%、~25%和~12%。同理可得,无ITO界面层的器件的Rdrift、Rsub和Rc分别为0.75 mΩ·cm2、0.31 mΩ·cm2和2.06 mΩ·cm2,分别占总RON,sp的~24%、~10%和~66%。图4(c)分别显示了有和没有ITO界面层的垂直GaN SBD的反向J-V特征。有ITO界面层的器件击穿电压为1100 V,没有ITO的器件的VBR保持在1000 V,击穿电场强度约为0.6 MV/cm,与先进水平(0.4~1.5 MV/cm)相当,说明VBR和击穿电场强度主要受He离子注入终端的影响,ITO界面层对其影响不大。

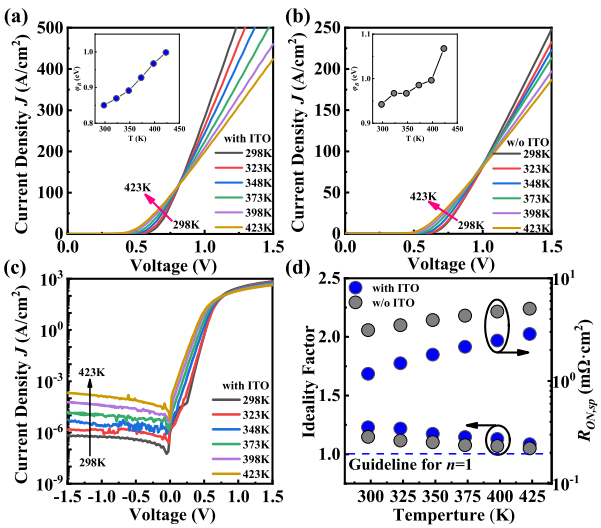

图5(a)显示了变温下(温度从298 K到473 K)有ITO界面层和(b)无ITO界面层器件的正向J-V特性曲线,插图为计算出的肖特基势垒高度与温度T的函数。(c) 显示了变温下(温度从298 K到473 K)有ITO界面层器件的反向J-V特性曲线。(d)理想因子n和RON,sp与温度T的函数。

如图4(d)所示,制备的氮化镓SBD器件也表现出良好的电学特性,有ITO界面层的器件开关比高达1.1×109,无ITO界面层的器件开关比为3.7×108,其中开关比定义为器件在电压为1.5和−1.5 V时对应电流的比值。图4(e)和4(f)显示了在2英寸晶片上制备的有ITO界面层器件沿X轴和Y轴的25点测试图。其中,VBR的实测值符合正态分布,表明制备工艺的均匀性和稳定性较好。

图5(a)和5(b)分别显示了从298 K到473 K的GaN SBD的正向J-V特性。随着温度的升高,两种器件的理想因子n随温度的升高而降低,电阻RON,sp增大。计算得到的肖特基势垒高度作为温度T的函数如图5(c)所示,有ITO的器件在298-473 K之间测量了与温度相关的反向J-V特性。随着温度的升高,电子获得了更高的能量,并且更容易克服SBH,因此器件的反向漏电流逐渐增加,说明TE模型主导了漏电流。该器件在298-473 K的温度范围内表现出很强的稳定性。在低电流水平下,两种器件的电流传导机制都遵循TE模型。两个二极管的理想因子n和RON,sp作为温度T的函数如图5(d)所示,可以清楚地看到RON,sp随着温度的升高而逐渐增大,理想因子n随着温度的升高而逐渐趋于1。这个受到TE模型的影响。n值越接近1,越证明TE是低电流水平下的主要导电机制。Fu等人为TE模型提供了SBD的正向J-V关系。

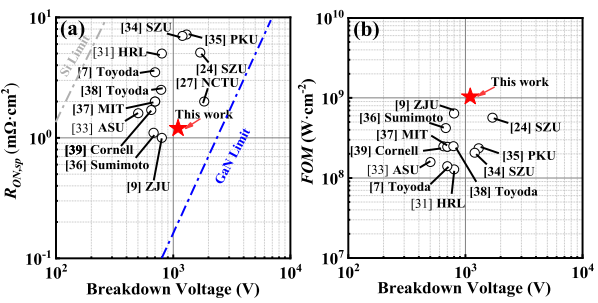

图6(a)显示了垂直的GaN SBD的VBR与RON,sp基准图。与其他报道的垂直GaN SBD相比,本工作中使用ITO界面层制备的器件更接近GaN材料的理论极限,同时表现出低RON,sp和高VBR。图6(b)显示了本工作中的VBR与FOM(VBR2/RON,sp)以及其他先进的GaN SBD对比。本研究中报道的GaN SBD的FOM为1.04×109,在已知阳极尺寸下,该工作报道了最低的ρc和最高的FOM~1.04×109。

4.结论

综上所述,我们首次制备了具有超薄ITO界面层的垂直GaN SBD。ITO界面层可以有效地缓解FLP效应,并在界面处实现了较低的功函数。这样,在N极性面GaN实现了高质量的欧姆接触,有效地降低了RON,sp。这项工作报道了在已知阳极尺寸下最低的 ρc~7.36×10-5 Ω·cm2和最高的FOM~1.04×109,该技术也显示出了垂直GaN SBD的发展的巨大潜力。

该项目获得国家自然科学基金资助(61974144和62004127)、广东省重点研发项目(2020B01010174003)、广东省杰出青年科学基金(2022B1515020073)、深圳科技基础研究项目(GJHS20190808112201662)。

- 8月10日将给大家带来“ 材料和器件的品质及成本管控先进技术方案”的线上主题论坛,助力我国碳化行业的技术演进。报名链接:https://w.lwc.cn/s/Nbeum2

- 8月31日14:00于线上举办的“先进封装技术之设计、材料、工艺新发展”主题会议!期待您的准时上线参会! 报名链接:https://w.lwc.cn/s/zm6fAr

- 9月21-22日,厦门云天半导体将联合厦门大学主办“首届半导体先进封测产业技术创新大会”。目前招观招商正在火热进行中,听众注册:https://w.lwc.cn/s/qEzy63

| 上一篇:用X射线形貌技术检查Si... | 下一篇:降低 Ⅲ-Ⅴ 族外延成本... |