反向外延提高LED发光效率

2012-8-30 15:17:18

—————Z.Q.Li, Crosslight公司

在传统的LED发光受限于不良电洞掺杂,以及主动区域以外载子牵引的内部电场。Crosslight公司提出的解决之道是:在p型膜层开始器件生长,因为这样有助于在量子阱的载子捕集,并且开启了极化引起的电洞掺杂。

LED只有在高内部量子效率时产生优秀的性能,所产生的光子之于所注入的载子具有较高的比例。然而,确保氮化物LED操作于较宽电流范围是如此情况之下则具有其挑战性,因为在这一类组件中当驱动电流被提高时,内部量子效率会有下跌之趋势。

不确定性围绕在称为衰减 (droop) 的这个效率降低之成因上。其溯源是激烈辩论的主题,因为了解为何导致的这件事将有助于推动制作能够支撑固态照明革命之对抗衰减的LED结构。目前,若干团体将内部量子效率降低归咎于各种的欧杰机制(Auger mechanisms),而其它团体则指摘缺陷复合 (Recombination) 或漏电流。然而,没人会争辩 AlGaN电子阻障层 (EBL, electron blocking layer) 的加入实质地提升氮化镓LED的性能。

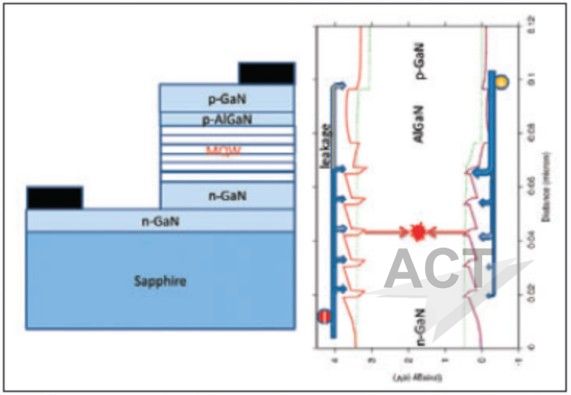

了解EBL好处的一个方式就是先看看它是如何在一个典型LED结构中运作 (参见图1)。在这个特殊的组件中,就如同任何其它的LED一样,尽可能藉由注入许多电子和电洞到量子阱 (QW) 使其效率最大化并使得在沟道 (trench) 里有效率非常好的复合。然而,比起电洞而言,由于电子有较小的有效质量和较高的移动率,电子有很高的可能性会跨过该QW区域而到达p掺杂区域,而不是在QW中复合发射出光线。漏电流不产生任何有用的光子,且大多数在QW以外的复合是非辐射的。

为了防止电子于QW区域脱离,工程师们可以加入一个p型AlxGa1-xN EBL以阻绝这些载子的前进:AlxGa1-xN的较大能带隙对于游移到QW区域外的电子其作用像是路障一样。然而,在氮化物材料中的电洞比电子重约10倍,其移动率大约是20~30分之一 。因此,电洞很少跨越过QW区域,导致在QW中电洞密度呈非均匀分布以致最终之较低的内部量子效率。

图1: 一个传统的p-side up氮化物LED以及显示出载子注入和复合之相应的电子能带图。电子向上游移到量子阱而电洞向下。具有较小有效质量的电子造成漏电流,然而具有较大有效质量的电洞在量子阱中产生非均匀的电洞密度。因此,呈现低的内部量子效率。

我们的努力显示出,增加铝成分和EBL的厚度可以更有效地阻绝电子。但还有一个问题-这些方法阻碍电洞移动,而结果是LED效率下降。

经由厚度,掺杂浓度和铝成分而最佳化的EBL在特点的关键数据上的改善是可以实施的。藉由实验的成果所呈现之完美组配将是非常昂贵和费时的,模块类的努力成果有更多的吸引力。像这样一个手法可使用我们已经位于加拿大不列颠哥伦比亚省的伯纳比所开发之Crosslight软件数值工具来加以实现的。我们的软件,已被广用于许多学术界和工业界的研究人员用以设计出LED的主动区和被动层,使用多维度的有限元素分析决定载子移动和在这些组件中的光学产生方式。所有针对氮化物半导体的重要特点能兼顾到,包括在异质接面极化电荷以及关于QW量子阱性质的不同晶体方向的影响。

LED的核心——多量子阱,EBL和接触层,通常是使用一维度的模拟设计,二维度和三维度模拟倾向使用于探讨和了解封装的相关议题,诸如热效应,电流分布和光的撷取。我们已经针对具有不同AlGaN EBL之一系列的组件去仿真LED性能。这些努力成果显示出,增加铝成分和EBL的厚度可以更有效地阻绝电子。但还有一个问题,这些方法阻碍电洞移动,而结果是LED效率下降。这个问题的一个理论解决方案是,提高EBL的p型掺杂密度,一个有效地增加电子阻障和降低电洞阻障的步骤。然这是不切实际的,因为在GaN类的材料中不容易获得非常高的p掺杂浓度。镁是常用的受体掺杂,其能阶是非常的高,在室温下,只有1%左右是解离且有助于电洞密度。添加实质量的镁到结构中是非常困难的,即使这是可能的话,会降低组件的特性。

Debdeep Jena和从印第安纳州圣母院大学的同事,发现了一个可能的办法来克服电洞掺杂议题。他们已经证实,具有正确等级铝成分的AlGaN膜层能够诱导由于这些材料本质极化的掺杂。这项技术有望解决关系到镁掺杂的许多困难点,因为极化引致的电洞掺杂并非热力上的激发所致。

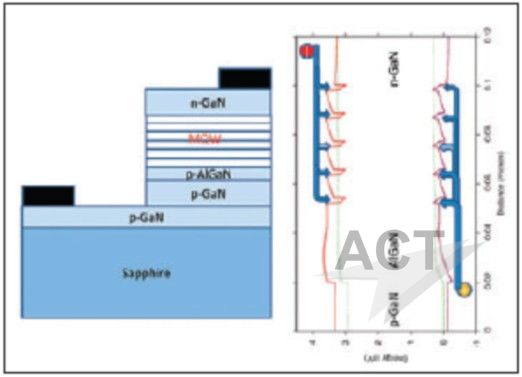

图2: 一种预期更高的输出功率和较低的顺向电压之新型p-side down氮化物LED。 具有铝成分分级10% 到15%的EBL膜层诱导在该层的掺杂密度。请注意到载子注入的方向相反,这有助于量子阱捕集电子并产生光子。

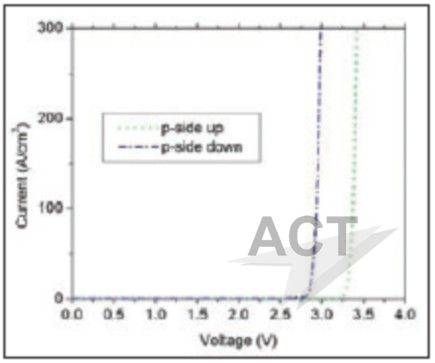

图3: p-side up和p-side down LED组件之电压和电流关系图。

反向外延层

传统上,LED的制作是藉由在基板上形成n型掺杂区域,并加上QW量子阱,ELB和p型掺杂区域 (见图1)。这个架构有一个主要的缺点:从介于量子阻障和区域外牵引载子阱之间的界面极化电荷所产生之电场,阻碍了在阱区之有效的载子捕集并导致高漏电流。

我们已证明,一种新型的p-side down LED架构可以满足这个问题。如此的组件,其特征有毗邻于基板的p型掺区域和n型区域于顶部区域,相较于传统结构使用反相电流注入来操作。(本LED的详细能带结构请参见图2)。

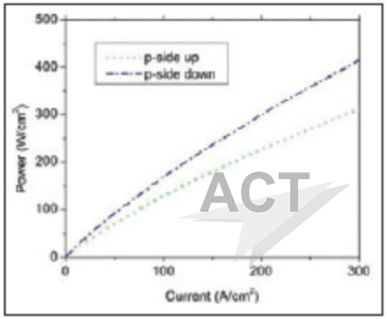

这种设计有两个好处:现在载子捕集比起脱离更为有利,归功于在电流方向的切换;电洞注入不需诉诸于过度多量的镁掺杂而有改善,因为藉由在结构底部置有EBL膜层,可以分级的方式,使极化引致掺杂增加电洞密度。我们的模拟结果证明,这样的反置架构使得LED的输出功率提增,还有减少其顺向电压。

图4: p-side up和p-side down LED组件之功率和电流关系图。

不幸的是,在真实组件上实现这种价值是不平凡的。由于镁,这是关系到MOCVD设备之最常见的p型掺质,杂质的扩散使得形成高质量的p-side down组件是需要技巧的。还应当注意的是,许多用于生产p-side down组件的技术,如Lift-off,将无法藉由我们的模拟而获得结果,因为他们翻转整个晶体 - 未能反转方向对应于晶体生长方向的电流注入。尽管如此,由于已知的氮化物外延技术之迅速提升,我们乐观地认为,高质量的p-side down组件将会在接下来的几年间现身业界。

扩展阅读:

J. Simon et al. Science 327. 60 (2010)

Z.Q. Li et al. J. J. Appl. Phys. 50. 080212(2011)

| 上一篇:氧化镓:挑战传统的宽禁... | 下一篇:硅器件与Ⅲ-Ⅴ族器件发... |