硅器件与Ⅲ-Ⅴ族器件发展路线图

2012-8-30 16:20:59

预计到2020年,硅晶圆代工厂将会从硅器件转向锗和Ⅲ-Ⅴ族器件。实现这一转变绝非易事,但是研究人员在电介质层、接触电阻、峰值电流、材料质量等方面不断努力寻求突破。理查德德·史蒂文森报道。

舆论曾一次又一次声称降低硅基晶体管尺寸的进程终有一天会终结。一些人认为,光刻尺寸不可能会超越光波长的界限——但是我们现在已经可以实现这一点;另一些人警告说,当晶体管达到纳米级别,电子无法获取足够的速度——然而只要在材料体系中施加应力就能迎刃而解;还有人指出高漏电流会限制器件尺寸的进一步降低,但是,诸如氧化铪等高K电介质取代氧化硅成为开关材料,使得这一难题也未能阻挡尺寸降低这一潮流的发展。

现如今,越来越多的评论家声称硅晶体管将会终结,这一次他们或许是对的。因为不仅是评论家们,众多的半导体行业从业者也相信这一点。国际半导体技术路线图(ITRS)就给出了到2015年半导体技术发展到11纳米时,锗和III-V族器件将会发挥重要作用。

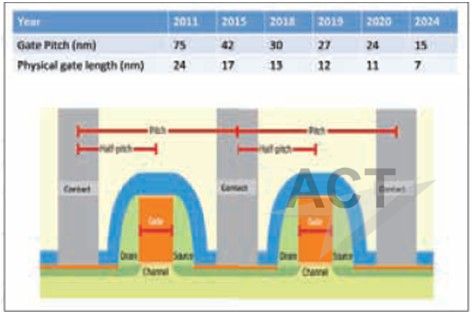

图1. 根据国际半导体发展路线图(ITRS)栅极间距节距的下降幅度超过了栅长的下降。

最近在德国法兰克福的欧洲 会议上,来自英国格拉斯哥大学的Iain Thayne对于新材料工艺对硅工艺生产线所能产生的实质的影响力给出了合理的解释。Thayne致力于研究Ⅲ-Ⅴ族的器件在射频及毫米波段前道工艺上的应用。他指出随着器件尺寸的降低引入 来提高性能是很有必要的。

Thayne说:“硅工艺中晶体管密度的增加导致严重的热效应,很快就会超越器件所能承受的极限。”他解释说,防止电路中的器件过热可以采纳新型的晶体管,在保证电路中电压降低的同时不会影响器件整体性能。唯一能满足这些要求的就是利用锗和Ⅲ-Ⅴ族器件来替代硅基晶体管。

他同时指出器件尺寸降低的关键就是增加器件上晶体管的密度。每一个新的节点都要求更短的栅长,但同时栅极节距也在不断缩短,缩短幅度反而更大。图1 中根据国际半导体发展路线图(ITRS)栅极节距的下降幅度超过了栅长的下降。

硅行业中持反对意见的业内人士则认为,Ⅲ-Ⅴ族器件无法匹配到逻辑电路当中。由于 中态密度较低,这类晶体管无法产生足够高的驱动电流。但Thayne的一位同事Asen Asenov则指出上述责难中的关键点所在。在Ⅲ-Ⅴ族器件当中尽管较低的态密度会导致较低的有效电容,然而这种材料体系具有较高的迁移率和较低的有效质量,使得注入载流子具有较高的速度并增强冲击电流特性。更重要的是,由于载流子能量高,低态密度意味着注入载流子具有更高的速度;由于载流子迁移率高,这类材料体系通过阻值调节可以在栅极调制方面具有更好的性能。

材料特性

为优化Ⅲ-Ⅴ族器件的性能,研究人员需要找到一种材料体系,能够将高速载流子和低工作电压器件结合起来。Thayne介绍到,栅极节距从75nm下降到15nm(2024年的目标值)意味着沟道载流子浓度将从8.5x1012cm-2 下降到5.1x1012cm-2,同时载流子速度从1.3x105ms-1 增加到3.5x105ms-1。这其中最有价值的材料是InGaAs,MIT的研究结果显示In0.7Ga0.3As作为沟道可以使载流子速度达到3x105ms-1,同时栅长可以降到20nm以下。

Thayne指出Ⅲ-Ⅴ族器件应用到逻辑电路中还需要更高的要求。他说这类晶体管需要具有75 mV/decade的亚阈值摆幅才能容易实现关断,还需要能够制成非平面器件结构,类似于Intel公司在22nm级中所应用的三栅极结构。此外由于尺寸降低,源极和漏极直接距离仅有几纳米,接触电阻将会意外上升。

格拉斯哥的技术团队同时参与了欧洲双层逻辑计划(European Dual Logic programme)以及半导体研究公司非典型CMOS研究中心(Semiconductor Research Corporation Non-Classical CMOS Research Center)的研究项目。他们的主要研究方向包括以下三个方面:栅层叠的提升;解决源极和漏极接触尺寸减小相关的问题;硅工艺和Ⅲ-Ⅴ族器件工艺流程兼容性的问题。

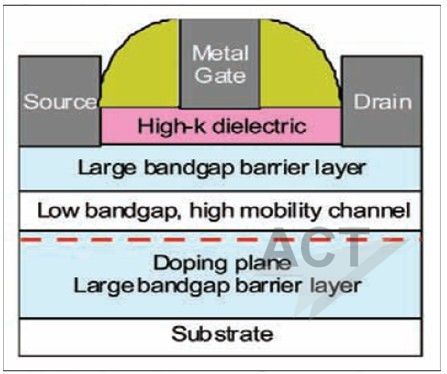

Thayne研究小组正致力于研发一种平带结构的MOSFET(如图2)。这是一种类似HEMT器件的结构,在宽带隙部分采用Delta掺杂,电子在迁移到窄带部分时会产生高迁移率的二维电子气。如果在介质层顶端采用功函数较高的栅极金属,器件就会形成耗尽,驱动其在零偏压下形成关断。加正向偏压载流子会重新注入到沟道中。

这种MOSFET具有两项关键优势:宽带隙低掺杂避免了短沟道效应;沟道非掺杂、界面漫散射低以及源极和漏极扩展区域较低的电阻所导致的高迁移率。

图2: 英国格拉斯哥大学的Iain Thayne研究小组开发了一种平带结构的Ⅲ-Ⅴ族器件。

该研究小组最初在2000年初开始研发该Ⅲ-Ⅴ族MOSFET时,他们一部分的主要工作是希望能制成良好的栅层叠。起初他们采用Veeco公司的第三代双腔室的MBE系统在半绝缘的GaAs衬底上来分子束外延研究团队外延层,样品在真空状态下由第一反应室转到第二反应室,在第二反应室中他们加入了Ga2O模板和GdGaO层。由这些外延片制作出来的平带Ⅲ-Ⅴ族MOSFET器件具有良好的性能,迁移率达到5000cm2V-1S-1,方块载流子密度达到2x1012cm-2以上,在1μm的栅长下跨导达到357μS/μm, 亚阈值摆幅为68 mV/decade。

为提高载流子的注入速度,研究人员尝试使用In0.53Ga0.47As作为沟道层, Al2O3作为介质层,厚度大约为60个原子层。这种新结构的好处在于可以增加迁移率,在掺杂浓度 2x1012cm-2 条件下,迁移率最高可以达到6000cm2V-1S-1。

对于表面沟道结构的晶体管而言,这种晶体管的栅长为1μm,Al2O3介质层厚度为2.5nm,晶体管的跨导达到357μS/μm, 但同时亚阈值摆幅可以达到150 mV/decade。

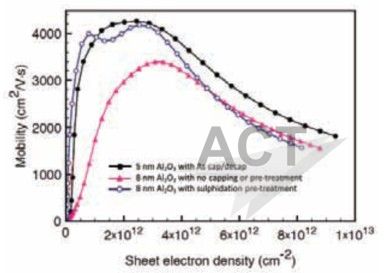

图3: 德尔研究院的研究人员开发的一种硫化工艺,通过去除砷盖层来最大程度上抵消迁移率下降的劣势。这是一项极被看好的技术成果,因为这是一种破坏原始界面的非平面晶体管结构。

Intel公司所采用的从平面晶体管到立体结构的转型给非平面器件指明了发展方向,即要求形成非原始态的界面。考虑到这一趋势的影响,Thayne与斯坦福大学的Paul McIntyre,德尔研究院的Paul Hurley组成研究团队一起共同研究不同的处理手段对晶体管性能的影响。

研究团队采用三种不同方式处理的外延片。其中两个在生长完Ⅲ-Ⅴ族外延层后从MBE反应腔中取出:一个不进行表面处理直接生长栅极介质层,如此空气中的氧化物会在介质层界面处产生;一个进行硫化工艺处理然后沉积高K系数的介质层。第三片在MBE系统中沉积一层防止氧化的砷盖层,然后利用斯坦福大学的原子层沉积技术去除掉该盖层,使得栅极能够直接沉积在原始表面上。对这些MOSFET进行迁移率测试,结果表明硫化工艺处理可以做到和原始表面处理一样具有良好的界面态(见图3)。

Thayne和他的团队要解决的第二个问题是要使得源极和漏极在仅有几纳米维度下具有较低接触电阻。ITRS路线图表明栅极节距要从2011年的75nm下降到2024年的15nm,这种情况下源极和漏极接触从21nm削减到2nm,源-漏之间的电阻要从160Ωμm下降到110Ωμm。

“传统”的方法是无法实现的,因为模拟以及实验都论证了在接触面积达到几个纳米时接触电阻会急剧上升。很多研究小组试图通过不同方式来解决这道难题。来自格拉斯哥大学的研究人员采用NiInAs来制备超低阻值浅金属化的源-漏级。Thayne表示这种首次采用的源-漏极技术可以最大程度满足ITRS所提出的12nm技术节点的要求,即相应的栅极节距在27nm。

格拉斯哥大学研究小组要解决的第三个问题是硅工艺和Ⅲ-Ⅴ族器件工艺流程完全自对准的兼容性。研究团队首创了两种不同的设计方案:‘栅极优先’和‘栅极替换’。前一种结构是采用In0.3Ga0.7As的平带MOSFET结构,采用GaO/GaGdO为介质层,栅长为100nm。这种晶体管漏极峰值电流达到250μA/μm,跨导达到150μS/μm,同时亚阈值摆幅达到150 mV/decade。‘栅极替换’结构下亚阈值摆幅降到130 mV/decade,并且由于具有高达18kΩμm的接近电阻,器件会保持持续的导通状态。这个问题可以通过源-漏级退火来解决,需要在一个小型设备上完成材料扩散。

三维器件

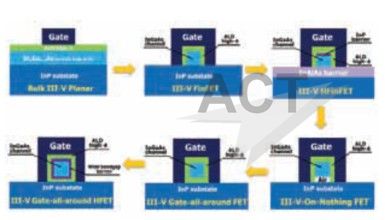

来自普渡大学的Pelde Ye的研究小组,沿用了Intel的技术路线,将三维技术引入到Ⅲ-Ⅴ族MOSFET中。Pelde Ye详细描述了FET的技术发展方向,从Ⅲ-Ⅴ族平面体材料结构发展到Ⅲ-Ⅴ族栅极包裹的HFET结构(见图4)。他的研究小组最近完成了后一种结构的器件制备。在InP衬底上制作p型掺杂的InGaAs沟道层多种多沟道结构,并将其埋在10nm厚的Al2O3,或者更厚的WN介质层下(见图5)。这其中一种具有4平行沟道,栅长50nm,fin宽30nm的结构可以产生较低的栅极电压,峰值电流达到1170250μA/μm,同时亚阈值摆幅达到150 mV/decade。

图 4:来自普渡大学的Pelde Ye指出,Ⅲ-Ⅴ族MOSFET已经从平面结构进化到一种电介质层包裹沟道层的结构。

这些研究成果必将对ITRS路线图产生深远的影响。传统上的栅长降低会使得电流已经跨导上升明显。而这些晶体管结构则会避免这种短沟道效应。更重要的是,由于量子限制,仅有纳米尺寸的沟道尺寸降低会导致电流的骤升。

最近电子学快报报道了Ye的研究成果的一些细节,他和他的研究团队发现当纳米线宽度从50nm下降到30nm时,电流上升40%,迁移率和跨导则分别上升34%和20%以上。

为了解释纳米线减薄造成电流上升——我们所不希望见到的负面效果,Ye的研究小组采用Synopsys公司的Sentaurus工艺器件仿真软件来模拟器件结构。模拟结果显示纳米线的结构会形成反转效应,即纳米线边缘的电子浓度低而内部电子浓度高。由于这些电荷载流子倾向于偏离散射作用较强的界面,电子就会在以更快的速度穿过沟道区。模拟结果随着纳米线尺寸的下降纳米线中间的电子比例上升,尤其到纳米线宽度下降到10nm时电子浓度下降的尤为显着。

整合到硅工艺上

如果 的MOSFET器件想要能够进行产业化,那他必须要能够整合到大尺寸硅衬底上。由于存在晶格常数以及晶体结构上的差异,锗和Ⅲ-Ⅴ族想要在硅上实现高质量的器件是非常困难的。来自比利时imec的Matty Caymax研究小组正尝试实现这一工艺。在2011年欧洲 会议上Caymax详细描述了为在硅上实现高质量的锗和Ⅲ-Ⅴ族器件所做的尝试和努力。Ⅲ-Ⅴ族器件的制作工艺上采用了一种杯状底部(更多细节参考“imec硅上Ⅲ-Ⅴ族器件制备工艺” imec prepares the ground for III-V transistors on silicon, Compound Semiconductor March 2011 p.12)。上述制备工艺(见图6)消除了能够导致器件产生缺陷的反相畴。Caymax说:“到目前为止我们最好的实验结果可以达到缺陷密度2x108cm-2,”他还说:“这还远远不够,我们会尽力实现更低的缺陷密度。”

一直以来晶体管的结泄漏都是比较严重的。为研究泄漏的起源,研究小组开发了一种截面原子探针扫描,通过这项新技术研究小组发现一些原子跑到了他们原本不该待的位置上:一些锗原子进入InP中,而一些铟和磷原子则跑到锗及硅衬底当中。

Caymax的研究小组,同之前提到的Thayne和Ye领导的小组一样,都在致力于将Ⅲ-Ⅴ族晶体管应用到未来的逻辑电路当中。到目前为止的研究成果让大家看到了曙光,棘手的困难也都在一步步的被克服掉。相信在将来若干年时间内,硅 CMOS 工艺一旦退出历史舞台,那么收拾残局并接手上台的必将会是这些 器件。

| 上一篇:棱锥结构引领单片式白光... | 下一篇:UV LED应用概况及市场发... |