低功耗 MOSFET的发展

2023/8/11 10:23:49 材料来源:雅时

刘建华,周霖,刘奇斌,迟延庆,上海积塔半导体有限公司

一、 前言

随着电动汽车的发展,汽车功率器件芯片也正在寻求能够有效处理更高工作电压和温度的组件。此时SiC MOSFET 成为牵引逆变器等电动汽车构建模块的首选技术。基于 的逆变器可使高达 800 V 的电气系统显著延长 EV 续航里程并将充电时间减半。据行业研究公司IHS Markit 的数据,到 2025 年,全球高达 45% 的汽车生产将实现电气化,每年将售出约 4600 万辆电动汽车。据估计,到 2030 年,这些数字将上升到 57%,每年的电动汽车销量约为 6200 万辆。功率器件正从Si基IGBT发展至SiC MOSFET时代。

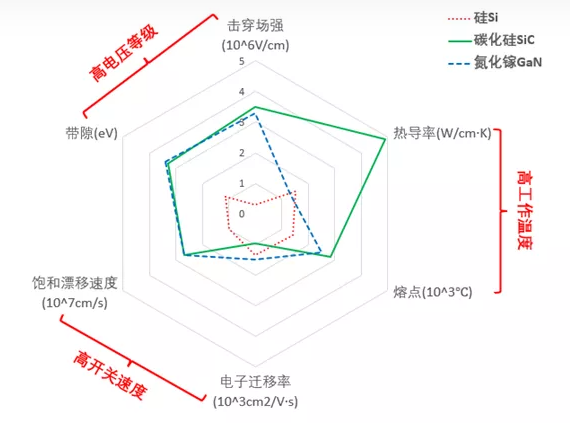

SiC的材料特性对比Si有了显著的提升: 材料的临界击穿场强为Si的近10倍,体迁移率与硅接近,带隙宽度是Si的3倍,电子饱和漂移速度是Si的2倍,热导率也为Si的3倍。 器件和相同电压档Si器件相比,厚度约为硅器件的1/10,理论上通态压降可以大大降低,在开关速率和开关损耗上优势则更加明显。

图1 SiC GaN与Si材料特性比较

图1 SiC GaN与Si材料特性比较

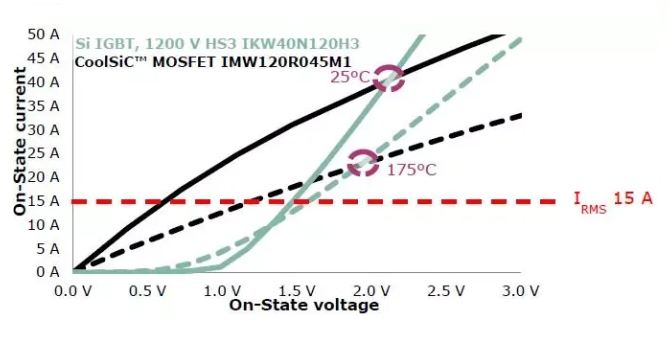

图2 SiC MOSFET与Si IGBT特性比较

图2 SiC MOSFET与Si IGBT特性比较

目前为止,SiC MOSFET在通态压降上并未对Si基IGBT表现出预期的优势。SiC MOSFET在衬底及外延层材料迁移率、SiC/SiO2界面表面迁移率方面的表现还有足够的提升空间。图2中显示了SiC Cool MOS与Si IGBT导通损耗的对比。

二、 MOSFET器件比导通电阻的优化

降低 的比导通电阻,影响比导通电阻有以下几个因素:

1. MOSFET的迁移率

根据在MOSFET中的位置可以分为沟道迁移率和体迁移率:当MOSFET导通时,栅极下方的沟道内的迁移率我们称之为沟道迁移率;在远离栅极和材料表面的区域,我们称之为体迁移率。

沟道迁移率可通过测量MOSFET的输出特性来得到:这里又可以将其分为(1)有效迁移率;(2)场效应迁移率;3)饱和迁移率。

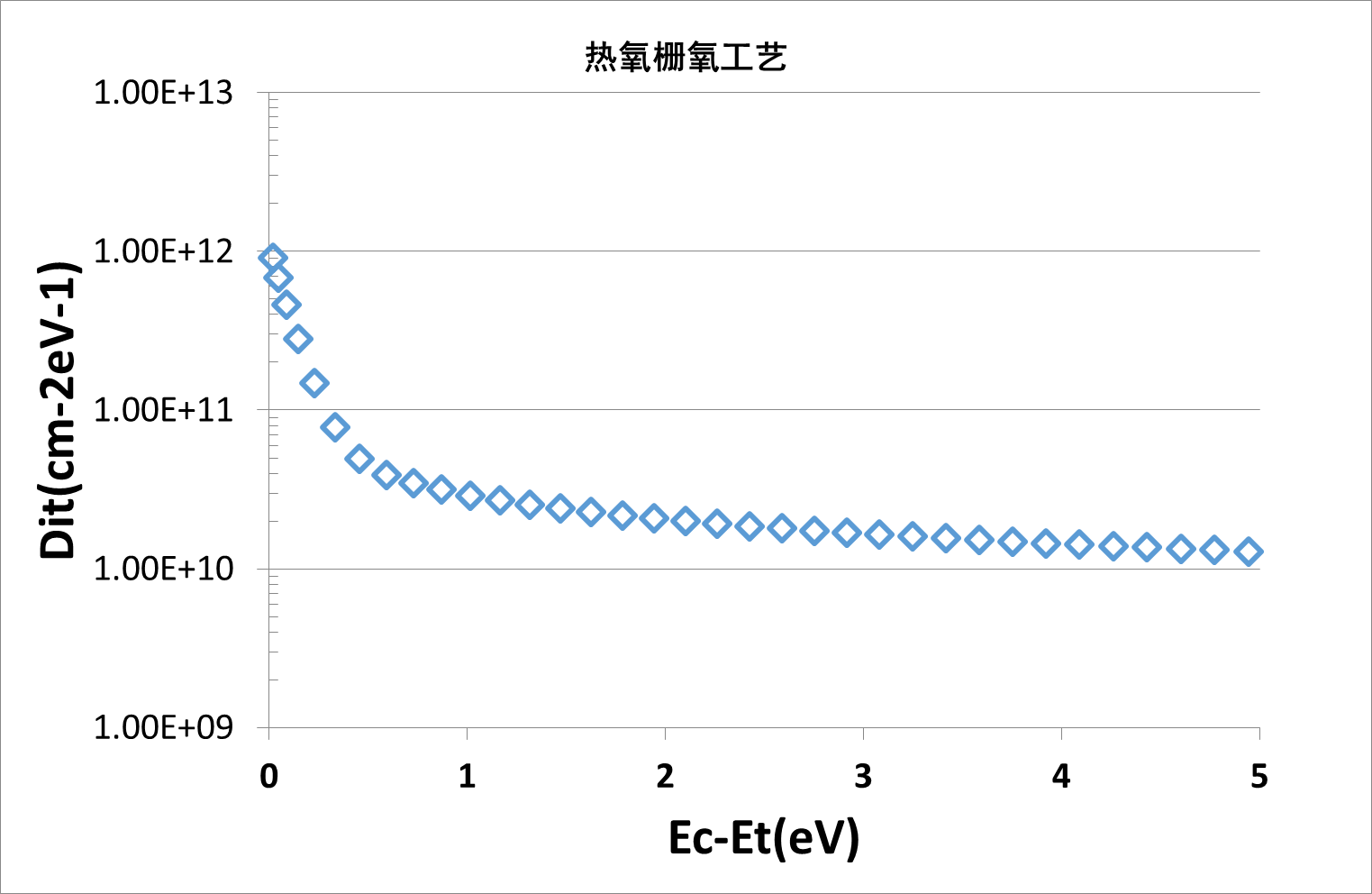

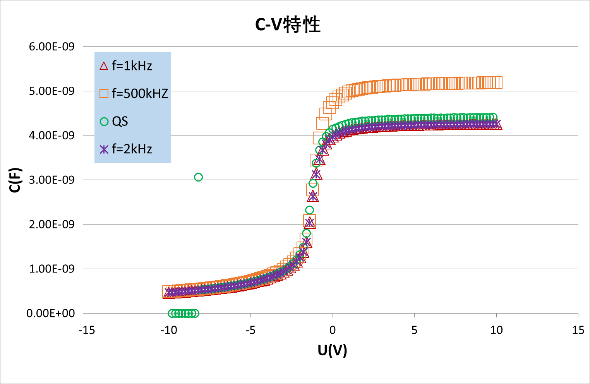

沟道迁移率受到SiC/SiO2界面处的许多缺陷的限制,这导致器件的场效应迁移率比其霍尔迁移率低两个数量级。一般认为:SiC中Si的选择性氧化导致碳沉淀并在SiO2中形成碳团簇(C-cluster),从氧化动力学角度考虑界面的化学势发现,界面的动态平衡性(dynamic equilibrium)限制了很高的碳化学势,从而导致了界面C-cluster缺陷具有较低的形成能,解释了高的界面态密度的成因,而其缺陷能级位置靠近SiC的导带底,因此降低了载流子的迁移率。热氧栅氧工艺形成的一组C-V特性曲线及界面态电荷量,其能级靠近导带底附近:

图3 热氧工艺下的界面态分析

图3 热氧工艺下的界面态分析

图4 热氧工艺下的C-V特性曲线

图4 热氧工艺下的C-V特性曲线

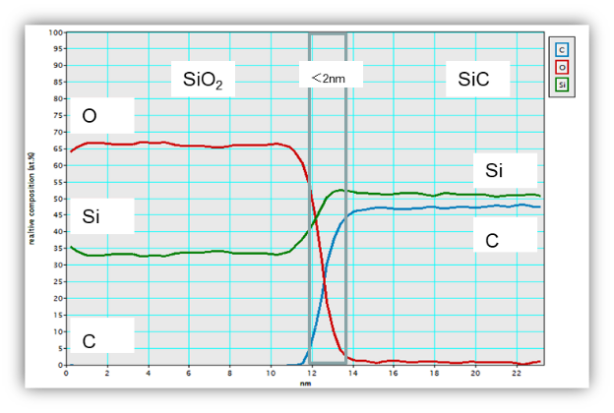

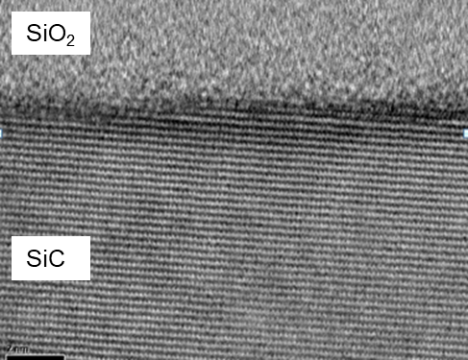

图5 热氧工艺下的界面EELS组分分析

图5 热氧工艺下的界面EELS组分分析

图6 热氧工艺下的EELS分析二维

图6 热氧工艺下的EELS分析二维

在SiC/SiO2界面,EELS强度分布中,测量点垂直于界面扫描,分辨率在1nm以下,所有的Si、C、O信号强度在界面处都表现出相当突然的变化,在EELS的分辨率下没有观察到C原子在界面附近的积累,也没有观察到明显晶格的无序或厚过渡层,所以假设存在过度层,厚度也小于2nm。

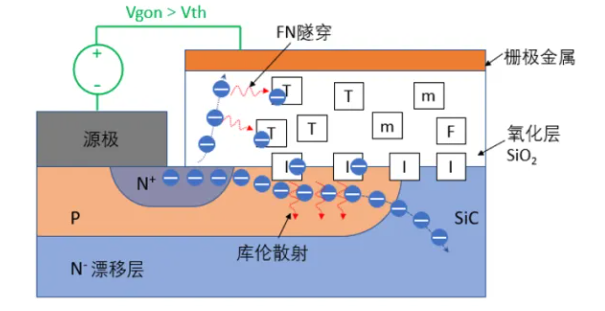

SiC MOSFET反型沟道电子主要散射机制包括:界面态电荷的库伦散射、体晶格散射、离化杂质库伦散射、表面粗糙散色以及表面声子散射。下图为SiC MOSFET沟道处的电子散射情况:

图7沟道处电子迁移率影响因素

图7沟道处电子迁移率影响因素

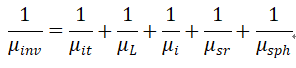

分别使用![]() 来表示,反型沟道迁移率为:

来表示,反型沟道迁移率为:

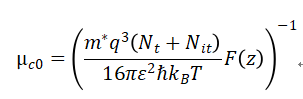

4H-SiC界面处主要由类受主缺陷对器件性能产生影响,库伦迁移率决定于界面陷阱对沟道电子的散射,Potbhare等人提出了一个准二维库伦迁移率模型:

式中q为单位电荷,KB为玻尔兹曼常数,m*为态密度有效质量,Nt为固定氧化物电荷数面密度,Nit为界面陷阱电荷数,![]() 为普朗克常数,ɛ为界面介电常数,F(z)为形状因子。

为普朗克常数,ɛ为界面介电常数,F(z)为形状因子。

另外Lombardi等人也给出了表面粗糙散射的迁移率的表达式:![]() ,其中a和LSR为拟合参数。

,其中a和LSR为拟合参数。

以上模型均和SiC MOSFET的沟道迁移率相关,在降低比导通电阻方面,平面SiC MOSFET中JFET的电阻、MOSFET体电阻以及高浓度衬底电阻也为总的比导通电阻提供了相当的贡献。在降低JFET电阻方面,出现了从平面MOSFET向Trench MOSFET的过度。

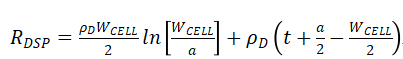

2. 器件结构设计优化降低比导通电阻

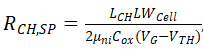

其中沟道电阻: ,其中

,其中

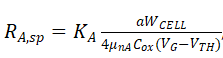

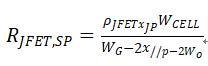

积累电阻: , JFET区电阻:

, JFET区电阻:

漂移区电阻为:

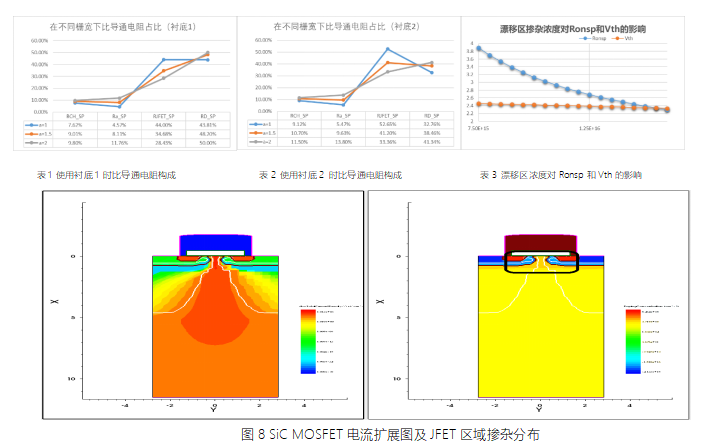

以一颗pitch 5.0um的SIC MOSFET为例,栅氧化层厚度约450A,Vth~3.0V,LCH=.5um,改变栅宽来调整a的数值,在a=1um,1.5um,2um条件下 ,以JFET平均浓度5X1016,漂移区厚度约10um时:

外延层厚度和掺杂浓度一定的情况下:降低JFET区电阻、并优化电流扩展区浓度对降低总比导通电阻贡献较大,RDsp与器件衬底状态相关性高,需达到外延掺杂浓度和厚度的折中设计。减薄衬底厚度:当减薄厚度由175um降低到110um时,对于常见的1200V/80mohm SiC Planar Mosfet,预计导通电阻降低3mohm左右,换算成比导通电阻降低约0.13mohm.cm2。

3. Trench MOSFET取代planar MOSFET降低比导通电阻

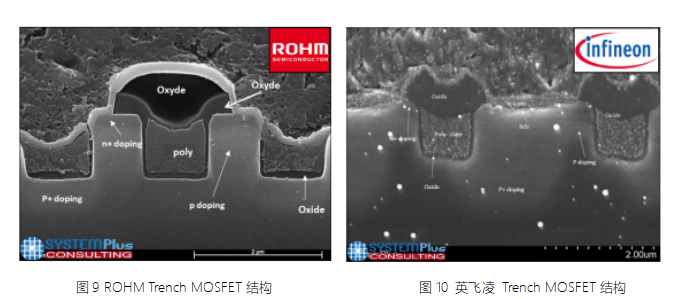

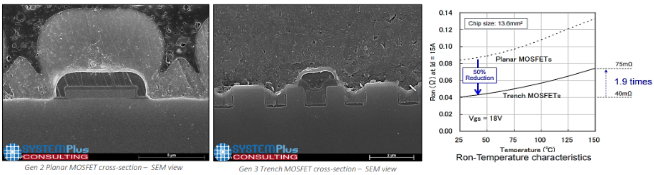

目前SiC MOSFET也正迎来从planar MOSFET向Trench MOS方向发展的趋势,Planar MOSFET JFET区域电阻在总导通电阻中占比较大,而Trench MOS理论上不存在JFET区域。

以ROHM代表的双沟槽结构和infineon为代表的半包结构代表SiC Trench MOSFET独立发展的两种结构。下图为ROHM公司从平面结构向Trench发展的Ron的表现。

图11 ROHM 平面与沟槽MOSFET结构对比即比导通电阻比较

图11 ROHM 平面与沟槽MOSFET结构对比即比导通电阻比较

三、主流产品的性能比较

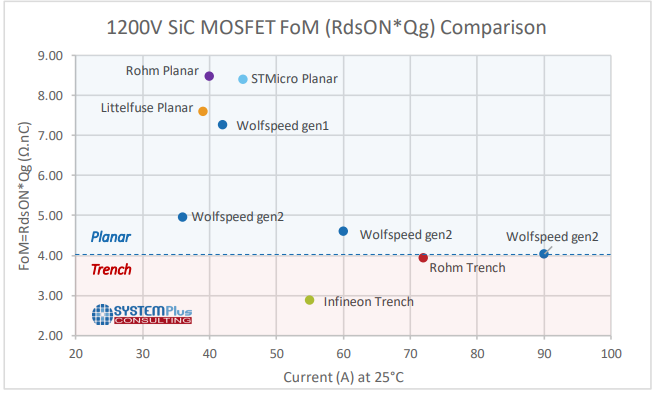

下图为目前市面上各主要大厂的MOSFET性能比较:

图12 各主要厂商SiC MOSFET比导通电阻比较

图12 各主要厂商SiC MOSFET比导通电阻比较

四、结论

MOSFET以低损耗,高阻断,高温工作,开关速度快等各优势,不过在技术方面:SiC单晶材料虽然在导致SiC功率半导体性能和可靠性下降的致命缺陷微管密度降低和消除方面近年来取得很大进展,但位错缺陷等其他缺陷对元件特性造成的影响仍未解决。SiCMOSFET器件目前存在两个主要技术难点没有完全突破:低反型层沟道迁移率和高温、高电场下栅氧可靠性。在 MOSFET克服以上问题后,将迎来爆发式的增长。

- 8月31日14:00于线上举办的“先进封装技术之设计、材料、工艺新发展”主题会议!期待您的准时上线参会! 报名链接:https://w.lwc.cn/s/zm6fAr

- 9月21-22日,厦门云天半导体将联合厦门大学主办“首届半导体先进封测产业技术创新大会”。目前招观招商正在火热进行中,听众注册:https://w.lwc.cn/s/qEzy63

- 11月1日-2日,雅时国际商讯联合太仓市科技招商有限公司即将举办“2023 先进技术及应用大会”。诚邀您相聚江苏太仓,筑创产业新未来。听众注册:https://w.lwc.cn/s/yqMZ7f

| 上一篇:降低 Ⅲ-Ⅴ 族外延成本... | 下一篇:控制SiC MOSFET阈值电压... |