3C-SiC增强GaN HEMT

2022/12/2 7:18:30 材料来源:

具有3C-SiC夹层的GaN-on-silicon HEMT具有相对低的传输损耗和非常高的击穿电压

具有3C-SiC夹层的GaN-on-silicon HEMT具有相对低的传输损耗和非常高的击穿电压

对于功率和RF应用的GaN HEMT的生产,硅衬底有其优点和缺点。它主要基于大型、低成本和广泛可用的平台,但它受到与外延层的显著热和晶格失配的影响,会导致高密度的位错和裂纹,影响器件性能、可靠性和寿命的缺陷。

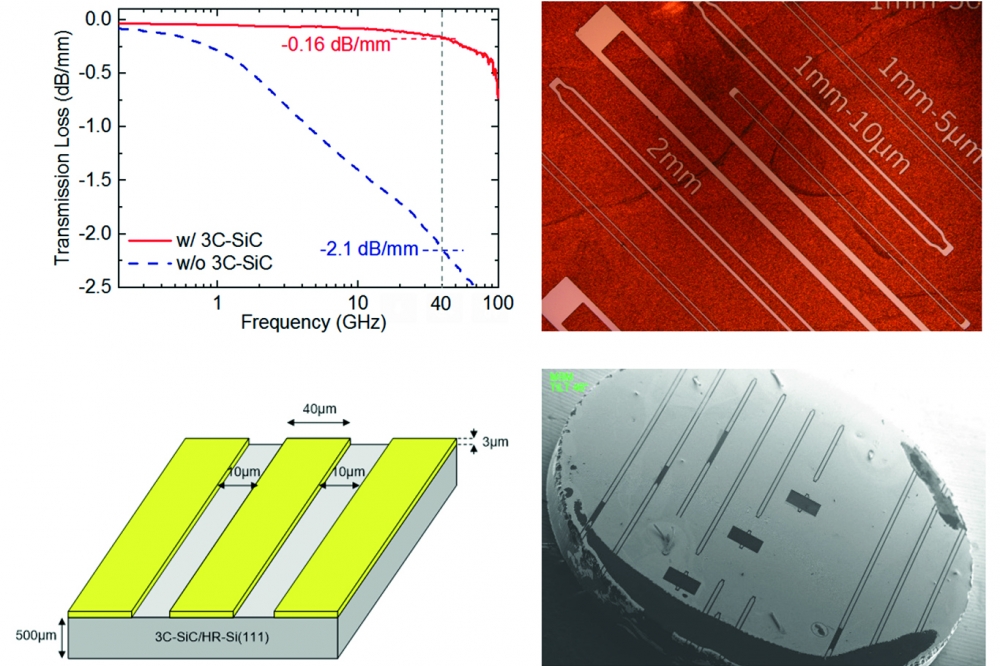

然而,通过插入3C-SiC夹层,似乎现在可以享受硅的好处,而不必承受缺点。国际合作的努力——由加拿大舍布鲁克大学的研究人员领导,阿尔及尔先进技术发展中心的研究人员支持;英国利物浦约翰摩尔大学;以及法国机构LIMMS/CNRS-IIS和IEMN/CNRS——已实现GaN HEMT在40 GHz下的制造,其传输损耗相对较低,仅为0.16 dB/mm,在1 µA/mm下的软击穿电压约为1530 V,据说是传统器件的三倍。

这项工作的基础是由Air Water Corporation生产的工程衬底,该衬底结合了500µm厚的高电阻率(111)硅和3C-SiC过渡层。Air Water Corporation自20世纪70年代以来一直致力于3C-SiC,并于1992年申请了GaN on 3C-SiC的第一项专利。

Brahim Benbackhti表示:“这家公司似乎在共掺杂3C-SiC方面有着丰富的经验,并实现了高质量的晶体结构和高电阻率。”Brahim Ben backhti代表该合作对Compound Semiconductor表示,他隶属于舍布鲁克大学和先进技术发展中心。

Benbackhti及其同事研究了在3C-SiC-on-silicon上以及仅在硅上生长的GaN基结构,以提供对照实验。他们已经制造并测试了由这两种外延晶片生产的一系列器件。

器件的缓冲层为3 µm厚的AlGaN层(用于对照),或沉积在1.7 µm厚掺钒3C-SiC层上的1.3 µm厚的AlGaN。在两个缓冲层上,该团队都添加了1.8 µm厚的Al0.18Ga0.82N背势垒、150 nm厚的未掺杂GaN沟道和4 nm厚的Al0.45Ga0.55N背势垒。20 nm厚SiN覆盖层的原位生长钝化了表面并防止了应变松弛。

MOS HEMT的源极至栅极间距为2 µm,栅极长度为1.5 µm,栅极至漏极距离为15 µm。使用共面波导的测量表明,插入3C-SiC夹层后,40GHz的传输损耗从2.1 dB/mm降至0.16 dB/mm。这一结果据说优于在由GaN、高电阻率硅或金刚石制成的衬底上获得的结果。

研究人员还研究了其晶体管的击穿电压。具有传统设计的器件显示出超过300 V的泄漏电流增加,在395 V时泄漏电流达到1 µA/mm。相比之下,具有3C-SiC夹层的变体需要超过1.5 kV的漏极-源极电压才能达到该值。

Benbackhti告诉Compound Semiconductor,可靠性是具有3C-SiC夹层的GaN基器件大规模商业化的最大障碍。“因此,需要研究器件在不同电应力和热应力下的性能及其寿命。

迄今为止,具有3C-SiC夹层的GaN HEMT已被证明是功率开关的良好候选者。Benbackhti评论道:“对于RF功率电子器件来说,至关重要的是检查3C-SiC夹层引入的热阻,这可能会起到热屏障的作用,并限制器件在RF中的性能。”

参考文献

A. E-H. Khediri et al. Appl. Phys Lett. 121 122103 (2022)

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

| 上一篇:通过转向1700V SiC MOS... | 下一篇:将透明导电氧化物引入深... |