III-V族与硅结合用于后5G时代的前端模块

2020/7/14 10:23:00 材料来源:CSC

整合深宽比捕获与纳米脊工程技术,可以实现300mm基板上的GaAs/InGaP HBT制造平台,用于放大毫米波产能。

Abhitosh Vais, IMEC

对于首个第四代的移动通信技术,传输频率的变化是逐步进化,而不是完全改变。工作频率已从低于1GHz升高至数GHz,带宽也从几十千赫兹扩展到数十兆赫兹。

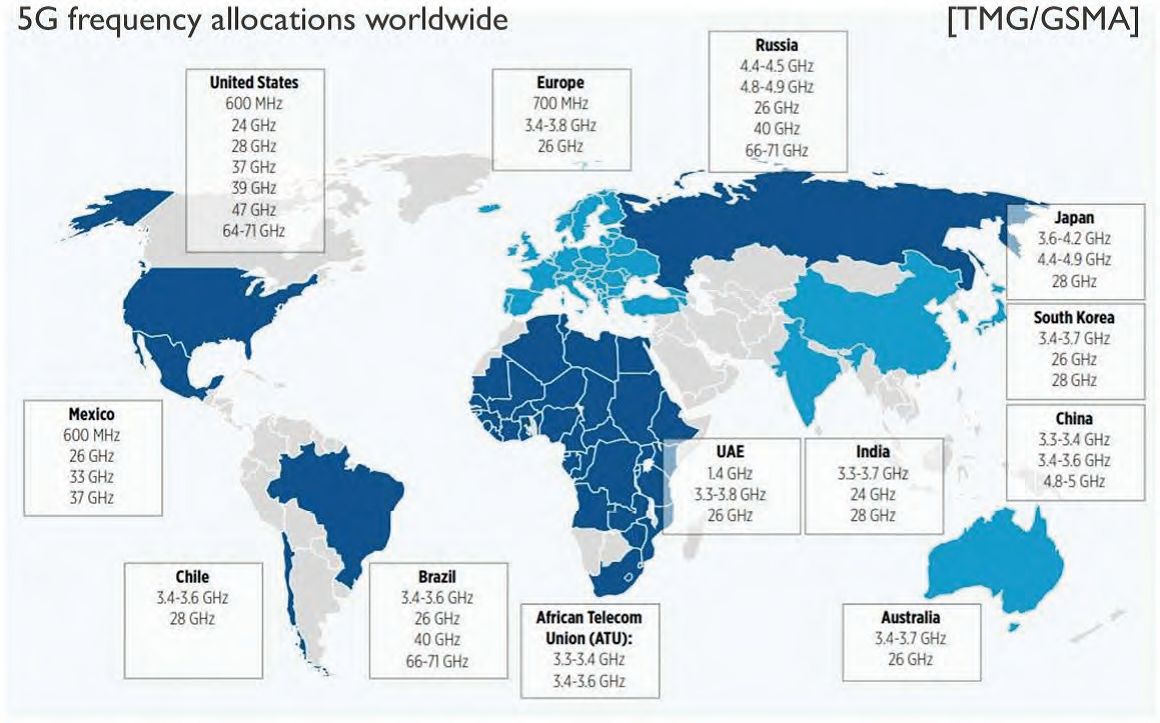

从这些角度来看,5G与以往相比是一个根本性的偏离(见图1)。它仍将涉及几GHz频段(称为6GHz以下频段)的传输,但除此之外,它将使用毫米波频率,这是解决当前频段带宽限制所必需的措施。

图1. 全球5G部署的频段分配。[TMG/GSMA],https://www.gsma.com/spectrum/wp-content/uploads/2019/10/mmWave-5G-benefits.pdf

使用毫米波频段(例如以28GHz和39GHz为中心的频段)的缺点之一,是它们的衰减要大得多。为了解决这个问题,需要引入小型蜂窝网络,以及新设计的手机,从而导致前端设计的复杂性增加。

当今手机的关键部件是GaAs/InGaP HBT,这是在昂贵的GaAs衬底上制造的。这类晶体管用于制造功率放大器,功率放大器具有单独的模块,每个模块覆盖不同的频带。

随着在毫米波域中运行的5G的推出,这些晶体管的RF性能必须保持,或者说甚至需要得到改善,同时还要降低成本,增加电路设计的灵活性,并降低功耗和减小芯片尺寸。不幸的是,现有的商业技术很难满足所有这些要求,从而来实现良好的RF前端模块,因此需要转向创新的材料和器件架构。

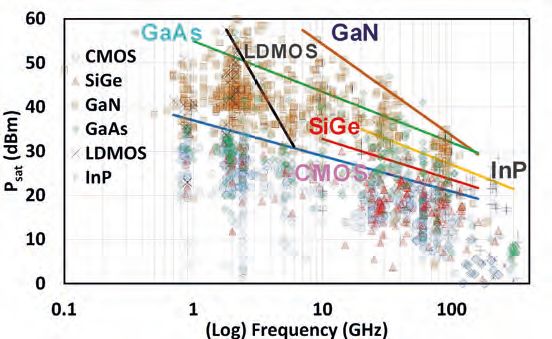

在imec,我们已经开发了III-V/CMOS混合技术,有望提供毫米波RF应用所需的小尺寸和低成本。它利用与III-V系统相关的功率处理和高频下的线性度(见图2),同时利用先进的CMOS后端处理工艺来实现复杂的控制电路。更重要的是,由于采用了共集成技术,因此有可能提高整个电路的能源效率,从而实现可以大规模生产的高能效、低成本毫米波技术。

图2. 不同技术相对于工作频率的输出功率Psat的技术趋势。 [[H. Wang, et al., “Power Amplifiers Performance Survey 2000-Present,”[online]。 https://gems.ece.gatech.edu/PA_survey.html]

将诸如GaAs之类的III-V族材料与硅结合起来的最大挑战之一,是较大的晶格失配。在晶格不匹配的衬底上外延生长会导致缺陷的产生,主要是穿透位错(threading dislocation)。这些缺陷会引起不希望的泄漏电流,从而降低器件性能。

一些研究小组试图通过在衬底和器件之间插入弛豫应变(strain-relaxed)的缓冲层,从而来降低这些缺陷的密度。然而,增加SiGe、锗或III-V族赝配(metamorphic stack)堆叠层会带来显著的额外成本增加,因为需要生长大于10μm厚度的这些材料,才能将缺陷密度减小到可接受的值。

无论采用哪种方法来创建CMOS/III-V技术,它都必须包括标准的硅衬底,以控制复杂性和成本。

深宽比捕获

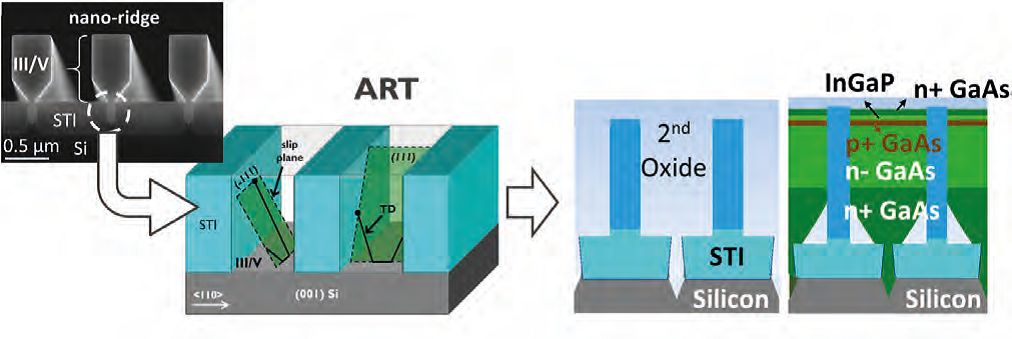

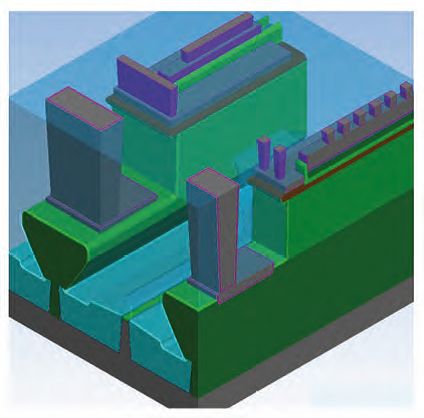

我们的方法结合了深宽比捕获(Aspect ratio trapping,ART——可以将缺陷限制在狭窄沟槽的底部)和纳米脊工程技术(nano-ridge engineering,这可以实现可用于制造器件的无缺陷III-V族材料体积的增加)(请参见图3)。使用完全兼容CMOS的流程对纳米脊进行进一步工艺处理,实现最后的器件(请参见图4),并最终实现与硅CMOS器件的共集成。

图3. 深宽比捕获(ART)和用于生长纳米脊的纳米脊工程示意性说明。注意,由于ART,穿透位错得以在狭窄的沟槽内被捕获,而在第二氧化物内部生长了相对无缺陷的纳米脊。

图4. 使用imec开发的CMOS兼容工艺流程,可以将III-V HBT集成在300毫米的硅晶圆上。

这种方法的优势之一是,它无需集成非常厚的缓冲层或者使用昂贵的衬底,就可以实现硅衬底和III-V族材料的集成。此外,我们可以利用我们在CMOS缩小尺寸和硅CMOS背景下开发的300mm硅上III-V族材料的专业知识。

我们通过在具有双氧化物结构的300毫米硅(001)晶圆上生长III-V族材料来生产纳米脊(见图4)。第一SiO2层是400nm厚的浅沟槽隔离(STI)模板。

这具有80nm宽的窄沟槽图案,底部为具有硅{111}面的V形沟槽。间距是800nm。在此之上,我们添加了第二氧化层,其厚度为1000nm。工艺处理之后,将在下面的窄沟槽中心形成600nm宽的沟槽。

使用选择性区域生长,我们将III-V族材料沉积在窄沟槽之中。硅与III-V族材料之间的大晶格失配会导致缺陷的产生,但由于其高的深宽比,它们被限制在该沟槽的底部。这确保了从窄沟槽中生长出来的材料是没有穿透位错的。

我们的下一步是转向纳米脊工程技术,从而实现纳米脊加宽,以便可以保持(001)生长面,从而实现平坦的界面。如果允许纳米脊工程生长自支撑结构,则会导致大的盒状形貌。我们通过添加第二氧化物模板来避免这种情况。一旦纳米脊到达第二氧化物,在器件有源区中的侧壁沉积就会降低。

在工艺完成的300mm硅晶圆上生长III-V族材料是在低压MOCVD反应室中进行的,该反应室使用了用于III和V族源的标准液体前驱体。通过加入四溴化碳和硅烷来实现掺杂。

注意,除了能够在硅上产生传统的盒状III-V族材料生长外,纳米脊工程还可以通过细致调整生长条件来产生不同的形状。这允许在纳米尺度上良好地控制纳米脊的轮廓。

缺陷表征

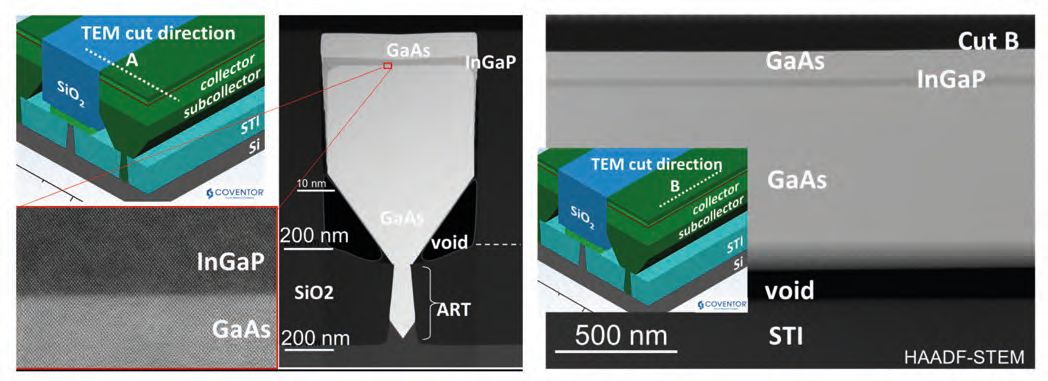

我们通过分析纳米脊中的缺陷密度来评估了我们方法的有效性。用于检查材料的最常见技术之一是透射电子显微镜。我们使用了称为高角度环形暗场扫描的形式。这种可以揭示沟槽缺陷的技术表明,III-V族器件堆栈中没有失配位错(见图5和图6)。尽管标准形式的透射电子显微镜在发现缺陷方面提供了更高的精度,但其扫描面积非常小,因此这种形式对于可靠地确定缺陷密度会非常麻烦。

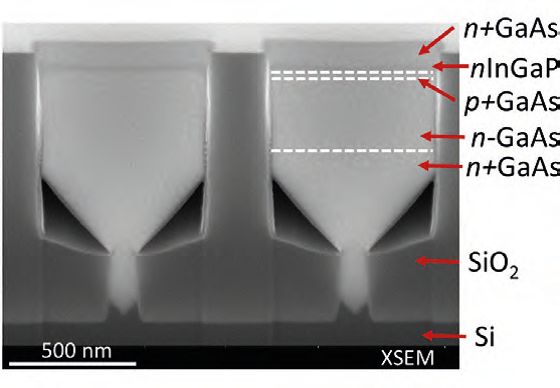

图5. 使用纳米脊技术在300mm硅衬底上生长的GaAs/InGaP纳米脊的截面扫描电子显微图(XSEM)。请注意,有源器件堆垛内部是没有缺陷的。

图6. 纳米脊整个宽度上(左)和纳米脊整个长度上(右)的高角度环形暗场扫描透射电子显微镜图像。

检查材料的另一种常用技术是电子通道对比度成像。这是用于生成统计相关数据集的相对较快的选项。使用该技术,我们发现GaAs纳米脊表面的穿透位错密度低于3×106cm-2。由于缺陷密度的值受检查面积的限制,我们设想GaAs纳米脊中的实际穿透位错密度甚至可能低于此值。

基于这一发现,我们知道了我们的纳米脊中的穿透位错密度足够低,可以防止其对我们的器件产生重大的影响。

具有不匹配晶格常数的外延系统也可能会有很多面缺陷。我们的方法将这种形式的缺陷捕获在平行于侧壁的{111}平面中,但是当面缺陷垂直于侧壁分布时,它们有可能最终在器件堆垛中终止。在此,其密度可能在0.14μm-1至0.45μm-1之间。不过,好消息是,由于面缺陷不涉及开放的晶体键或明显的应变场,因此与位错缺陷相比,它们对器件性能的影响较小。

300mm硅上的HBT

利用我们在硅上生长无缺陷III-V族材料层的能力,我们最近展示了在标准300mm硅衬底上的单片集成GaAs/InGaP HBT。这一成功为制造超越5G应用的InGaAs基器件奠定了坚实的基础。

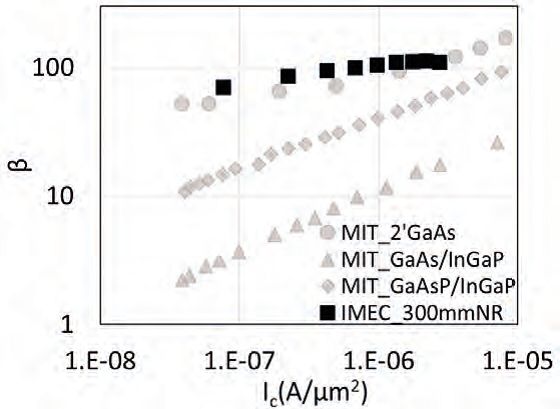

我们的突破是基于具有HBT特性的n-InGaP/p-GaAs/n-GaAs层的堆叠。发射极-基极和基极-集电极二极管分别显示出约1.2和1.4的理想因子,突显了这些结及其形成材料的优异质量。这种结构具有高质量材料的其他证据是直流电流增益超过110,集电极和基极之间的击穿电压为10V。

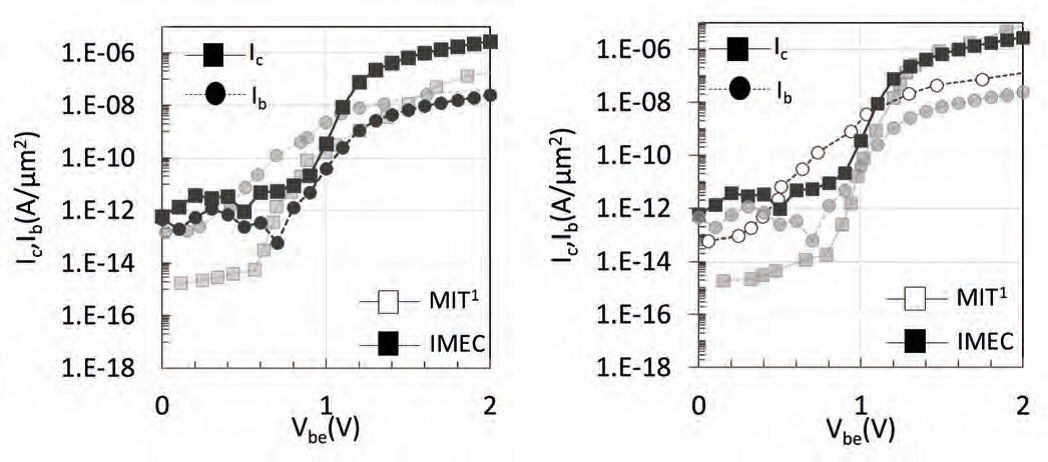

为了对我们的器件进行基准测试,我们将其传输特性与在2英寸GaAs衬底上形成的HBT和具有相似缺陷密度的厚应变弛豫缓冲层上形成的相似设计进行了比较(见图7)。令人鼓舞的是,我们的器件优于在厚缓冲器上制造的器件,其关键特性与在高质量2英寸GaAs衬底上制造的器件非常相似(见图8)。这一发现支持了我们的主张,即通过300mm硅上的纳米脊技术生产的材料,其质量已经足够使用了,我们不需要厚应变弛豫缓冲层或昂贵的衬底。

图7. 本项工作中所制造器件与具有应变弛豫缓冲层的参考器件[1](IEDM2019中展示)的电学特性(Gummel图)的比较。[1]C. Heidelberger et al. Journal of Applied Physics 123 161532 (2018)。

图8. 基于纳米脊工程的GaAs/InGaP堆叠上制造的HBT器件与具有应变弛豫缓冲层的参考器件[1](在IEDM2019上展示)的直流电流增益比较。[1]C. Heidelberger et al. Journal of Applied Physics 123 161532 (2018)。

由于我们已有的成功,我们对我们的技术寄予了厚望。它的优势之一在于它展示了III-V族材料和硅CMOS如何能够结合起来,从而为5G和毫米波应用服务。这可以通过在300mm硅衬底上使用InGaAs HBT来实现,这种组合可以在超越5G的RF应用中得到应用。

我们从混合III-V/CMOS技术的初期性能中获得了巨大的信心,该技术使该器件性能与在高质量GaAs衬底上制造的器件可以相媲美,并且我们希望在纳米脊技术方面做进一步的探索,以便能够发掘其全部的潜力。

| 上一篇:用于扇出型晶圆级封装的... | 下一篇:单晶圆工艺简化SiC的生... |