详细内容

制造更好的氧化镓晶体管

材料来源:compoundsemiconductor

用高导电材料包裹调制掺杂的Ga2O3 FET解决了有关热管理和载流子传输的问题

如果要使Ga2O3 晶体管发挥其在射频和电力电子领域的潜力,必须解决与低电子载流子迁移率和热量提取有关的问题。想要解决这两个问题需要以下机构的工程师通力合作,美国宾夕法尼亚州立大学、俄亥俄州立大学、Kyma 科技、 Modern Microsystems和犹他州立大学。

该团队正在研究用具有调制硅δ掺杂功能的FET(一种被称为MODFET的晶体管)代替MOSFET并采用高热导率的材料,使器件在不过热的情况下更高效地运行。使用最强大的散热结构可使功率处理能力提高5倍。

研究小组的研究包括实验研究和模拟。包括利用热反射热成像技术测定不同工作条件下MODFET的表面温度。为了验证这些结果,工程师们转向了纳米粒子辅助拉曼测温法。两种探测栅极金属温度升高的技术都给出了极好的一致性。在Synopsys Sentaurus和COMSOL Multiphysics软件产生的模拟中复制了该值。

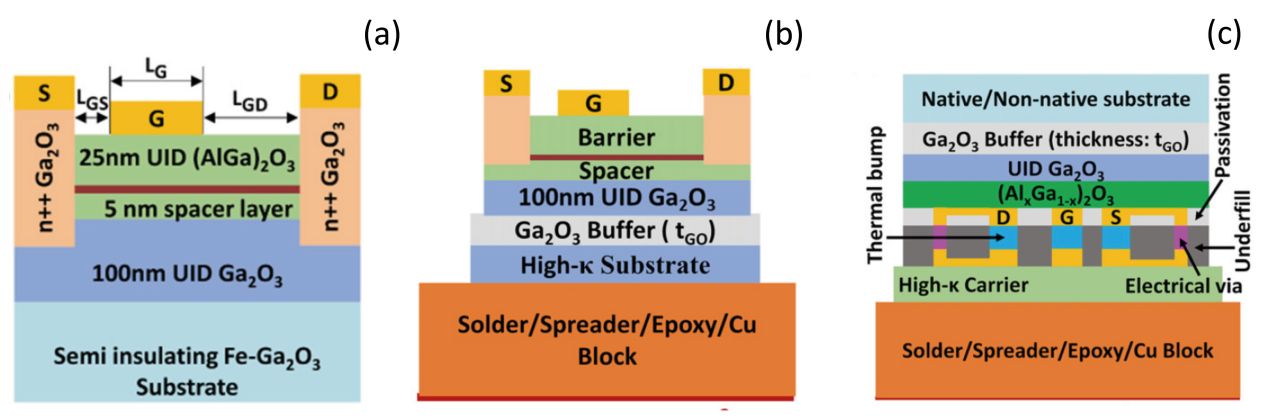

在考虑栅源间距为1μm、栅长为3μm的MODFET中栅漏间距的变化时,模拟被引入其中(见图a)。为了提高功率FET的击穿电压,设计人员倾向于采用超过栅源间距的栅漏间距。根据模拟结果,通过增加栅-漏间距,将热测量装置所用的栅-漏间距从3μm增加到20μm,使峰值电场降低了一个数量级。反过来,峰值温度的上升下降了近40%。

工程师们还利用模拟来考虑在MODFET下插入高导热基板对功率处理的影响。对于一个具有10μm厚的Ga2O3 缓冲层的MODFET (见图 b ),将该器件安装在4H-SiC晶片上,可使最高温度上升减少了46%。用热导率高出4倍左右的金刚石替代4H-SiC时,有进一步的改善。然而,增益是适度的,由于10μm厚的Ga2O3缓冲层主导了器件的热耗散,器件的最高温度仅下降了5%。

为了评估缓冲层在4H-SiC向金刚石转变时对器件发热的作用,课题组还模拟了Ga2O3缓冲层厚度分别为100μm和1μm的MODFET。对于前者,金刚石只比4H-SiC增长1%,而对于后者则是14%的提高。不过,研究小组很快指出,将Ga2O3缓冲层减薄到仅1μm的可行性还有待确认。

这些趋势的实验验证来源于红外热像仪的测量,并得到了有限元热模型的支持。工程师们证明,在具有10μm厚度的Ga2O3缓冲层的MODFETs中加入500μm厚的4H-SiC晶片,峰值温度降低了66%。

峰值温度的进一步降低可以源于双面冷却设计。在这种结构下,最好的结果来自以下组合:在FET上沉积纳米晶金刚石;使用金凸点,而不是铟,并将晶体管安装在多晶金刚石上。

模拟结果表明,对于运行在200℃沟道温度下的MODFET,从传统的同质外延设计过渡到最佳的双面设计,可使功率密度从1.7W/mm提高到9.5W/mm。

参考文献:

'Electro-thermal co-design of β-(AlxGa1-x)2O3/Ga2O3?modulation doped field effect transistors'?by Chatterjee et al. Appl. Phys. Lett 117 153501 (2020)

| 上一篇:CMOS对阵铟镓砷SWIR传感... | 下一篇:美国团队取得钙钛矿的新... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk