详细内容

大幅降低高电压 Ga₂O₃ MOSFET 的导通电阻

材料来源: 杂志

具有场板结构的氧化镓MOSFET 集高击穿电压和低导通电阻于一身

氧化镓晶体管拥有巨大的潜力,有望将极高的击穿电压与高电流密度和高工作温度等特性组合在一起。

在所有这些方面均有所斩获是非常具有挑战性的,因为用于形成源极和漏极触点的旋涂玻璃(spin-on-glass) 和离子注入法需要采用高温退火工艺,而该工艺会将缺陷引入材料。但是,根据美国纽约布法罗大学的一个工程师小组最近的研究工作成果,通过转向使用分子束外延 (MBE) 工艺在沟道的顶部生长一个高掺杂覆盖层,是可以获得成功的。

这些研究人员多年来一直在开发Ga2O3MOSFET,他们最初的工作重点是提高击穿电压。2018 年,该团队取得了成功,将击穿电压的记录从 750V 提升到 1850V。由具有 20μm 栅长的器件创立的这个新标杆是引入场板、并在晶体管的周围添加 Flourinert 特制绝缘液体(以防止发生空气击穿)的结果。

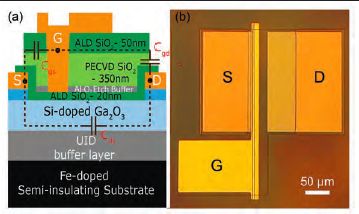

图:(a) 低电阻、高电压Ga2O3 HEMT 的结构,(b)制作出的器件的光学图像。

遗憾的是,这些器件具有非常高的导通电阻,而用于形成源极和漏极触点的高温旋涂玻璃在工艺中存在的可变性是造成这种情况的根源。如今,通过转为使用 MBE 工艺步骤,这个弱点已经被克服,而且并未牺牲击穿电压性能指标。这使得上述的两种触点可在低得多的温度下形成。

电子束蒸发增添了 Ti/Au/Ni 源极和漏极触点,通过在 520°C 温度下进行快速热退火降低了接触电阻。反应离子刻蚀去除了覆盖层,然后提供器件台面隔离。接着是 UV 臭氧处理,随后是栅氧化层的沉积。

氧化物的沉积是采用原子层沉积 (ALD) 和紧随其后的等离子体增强化学汽相沉积 (PECVD)工艺完成的。据该研究小组的发言人 Ke Zeng 表示,ALD 用于提高顶层氧化物强度,因为它提供了更致密和质量更高的薄膜。对 MOSFET 所做的测量显示:输出电流为 20mA mm-1,导通电阻为 520mΩ cm2。亚阈值摆幅为 1.5V dec-1(在10-6 mA mm-1 条件下),这表明界面状态密度为 2.8×1013 cm-2 eV。

虽然该团队降低了 MOSFET 的导通电阻,但是仍然大于其他研究小组报告的最佳值。Zeng 和同事们认为,这有可能是因为沟道中的掺杂较低、源极存取区的耗尽、界面状态密度高所致。

Zeng 说,他和同事们始终严重受困于界面陷阱问题,就是因为他们没有解决这个问题所需的足够时间和人力。

不过,他认为,通过在栅氧化层沉积之前采用某种形式的表面处理,能够解决此问题。可选方案包括富有进取心的湿法化学清洗和反应离子刻蚀,这些选项为使表面平滑进行了微调。

Zeng 相信,通过采用新的器件结构和特殊的处理方法,他所在的研究小组开发的 MOSFET 的击穿电压会更高,而且其导通电阻可以更低。

参考文献

K Zeng et al. Appl. Phys Express 12081003 (2019)

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

| 上一篇:在GaN VCSEL 中实现单模... | 下一篇:美国团队取得钙钛矿的新... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk