中科院微电子所在存内计算处理器上取得进展

2024/7/10 9:56:08 材料来源:雅时

存内计算(CIM)芯片相比传统冯诺依曼架构芯片在宏单元层级实现了高能效,但系统层级的复杂周边电路使得系统能效仍然受限,系统/宏单元能效比通常低40%,使其在面向神经网络和推荐系统应用领域仍然存在一些挑战。此外,对存储主导(例如推荐系统的嵌入层)的操作,需要大量的片外访问,由于嵌入表不能被完全存储到片上,即使采用内容可寻址存储器(CAM),仍会导致大量的片外访问和较高的片上CAM搜索功耗。

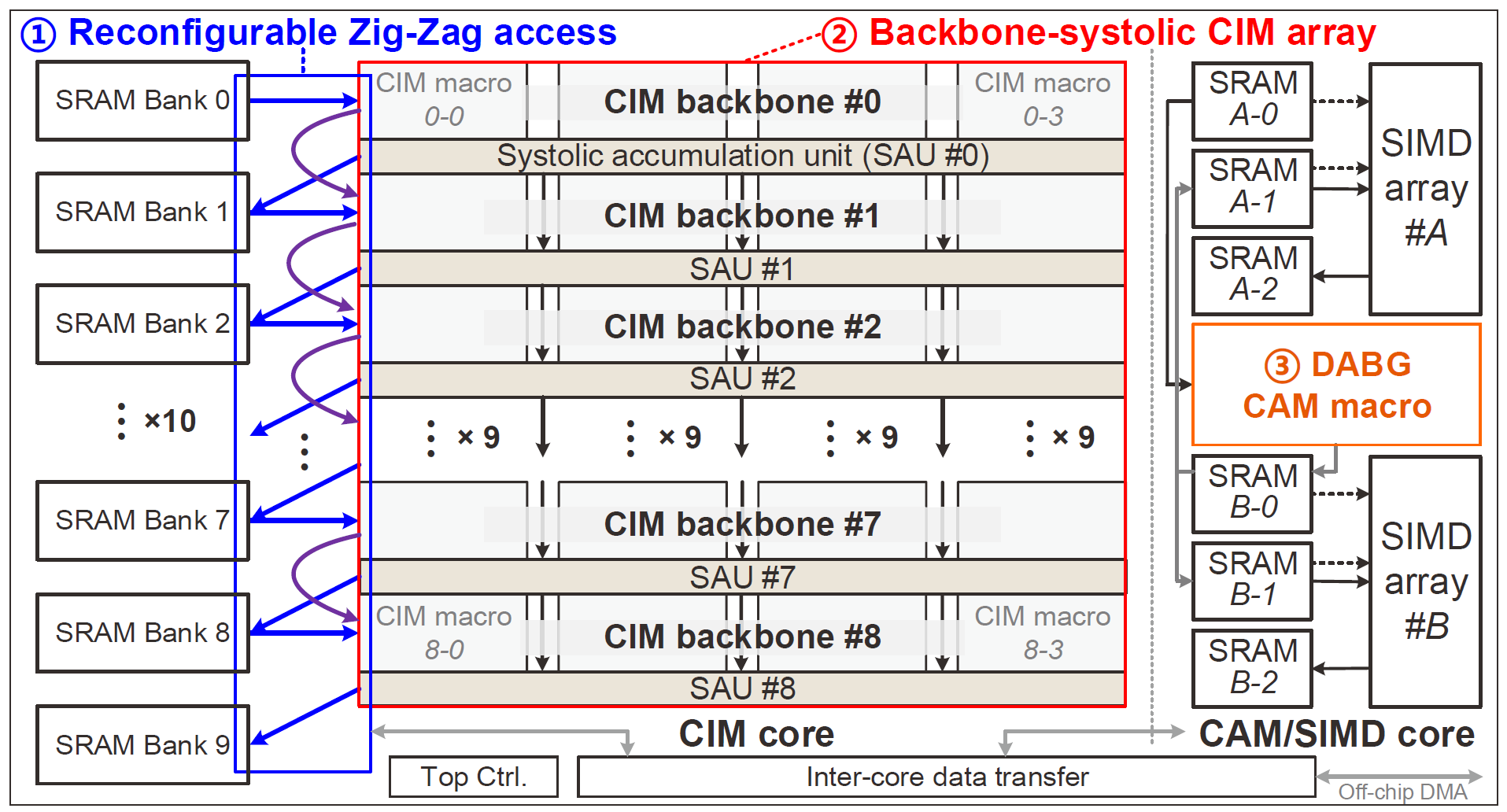

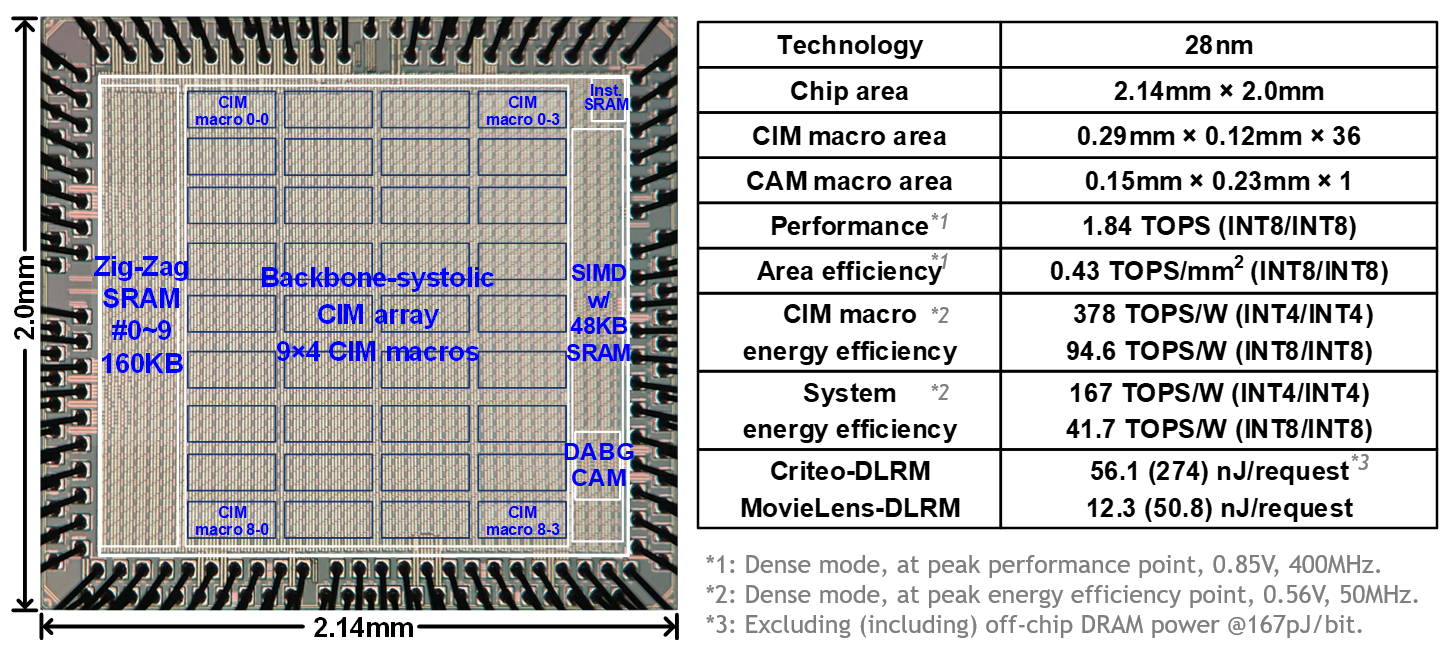

针对上述挑战,微电子所集成电路制造技术重点实验室刘明院士团队提出了一种具有Z型脉动阵列CIM 主干(backbone)和分块/分行自行关断(block/self-gating)CAM的存内计算处理器。本工作针对不同的卷积和矩阵向量乘法(MVM)操作,提出了一种可重构Z型存储访问结构和一种存内计算脉动阵列来提升系统/宏单元能效比。团队还提出了一种基于数据分布特性的分块/分行自行关断的CAM宏单元以减小片外访问和片上搜索功耗。该工作在28nm CMOS工艺下成功流片,对神经网络和推荐系统应用分别实现了37.9-81.5TOPS/W和12.3-56.1nJ/request的系统能效。

基于该成果的文章“A 41.7TOPS/W@INT8 Computing-in-Memory Processor with Zig-Zag Backbone-Systolic CIM and Block/Self-Gating CAM for NN/Recommendation Applications”入选2024年VLSI会议。微电子所博士生戴卓玉为第一作者,微电子所岳金山助理研究员和刘明院士为通讯作者。

图1:CIM-CAM处理器整体架构图

图1:CIM-CAM处理器整体架构图 图2:28nm高能效CIM-CAM芯片照片与关键参数

图2:28nm高能效CIM-CAM芯片照片与关键参数7月25日14:00,CHIP China 晶芯研讨会即将组织举办主题为“先进半导体量测与检测技术进展与应用”的线上会议。诚邀您上线参会交流答疑,推动先进半导体量测与检测技术的交流与碰撞,欢迎报名:https://w.lwc.cn/s/fuQBbu

| 上一篇:光子学市场反全球趋势而... | 下一篇:美国宣布拨款16亿美元,... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk