新技术发布!“万能离子刀”技术为8英寸SiC提供低成本方案

2024/4/15 9:21:59 材料来源:雅时

工作简介

近日,上海微系统所异质集成XOI课题组自主研发了基于“万能离子刀”的 (SiC)复合衬底制造技术,SiC晶圆尺寸最大达到8英寸,并初步通过外延验证。该技术将高质量SiC单晶薄膜与低成本SiC衬底集成在一起,在满足高质量外延需求的同时,预期将使8英寸SiC衬底制造成本降低40%以上。技术方案的实施有望加速SiC功率器件低成本化进程。

研究背景

材料作为宽禁带半导体中的代表材料,具有高击穿场强、高导热性和高载流子饱和迁移率等优异特性。在产业应用中,4H晶型因其优良的电学性能成为行业主要选择,是高频、高温、大功率电子及光电器件等应用的理想材料。典型的,在800V以上的新能源汽车应用中,SiC MOSFET与传统的硅基相比具有更高的电子迁移率、更高的开关速度更低的开关损耗及更小的器件体积,性能优势明显,但目前瓶颈则在于SiC功率器件较传统Si器件的成本高昂,解决的关键则在于降低衬底成本。通常,采用更大尺寸晶圆能够大幅度降低单个器件的成本,然而当晶圆从6英寸扩径到8英寸时,制备难度进一步增加,“切磨抛”良率大幅下降,衬底成本不降反升,这使得8英寸 晶圆制造面临极大的挑战。

上海微系统所异质集成XOI团队基于“万能离子刀”异质集成技术,通过离子注入剥离与转移的方法可以将高质量SiC单晶薄膜与硅、低成本或多晶SiC集成在一起,进一步循环剥离高质量SiC衬底(“刀削面”工艺),从而使高质量SiC一片变多片,实现单片成本的大幅下降。团队在国内最早开展SiC单晶薄膜制备与异质集成技术研究,率先在国际上实现并报道了4英寸Si基SiC单晶薄膜异质晶圆(SiCOI) [Optical Materials, 2020, 107: 109990],并在高温MEMS [IEEE Sensors Journal, 2022, 22(14): 13930-13936]、集成光子学[Light: Science & Applications, 2021, 10: 139;Light: Science & Applications, 2022, 11: 341]、量子信息[Applied Physics Reviews, 2022, 9: 031302]等领域付诸应用,相关研究成果发表于Appl. Phys. Rev.、Light Sci. Appl.、npj Quant. Inform.等高水平期刊上1-5。而在主流的SiC功率电子领域,“万能离子刀”技术预期在SiC晶圆成本降低及产能提升方面优势明显,预期将为行业发展高质量、低成本8英寸SiC技术提供一种创新解决方案。

工作内容

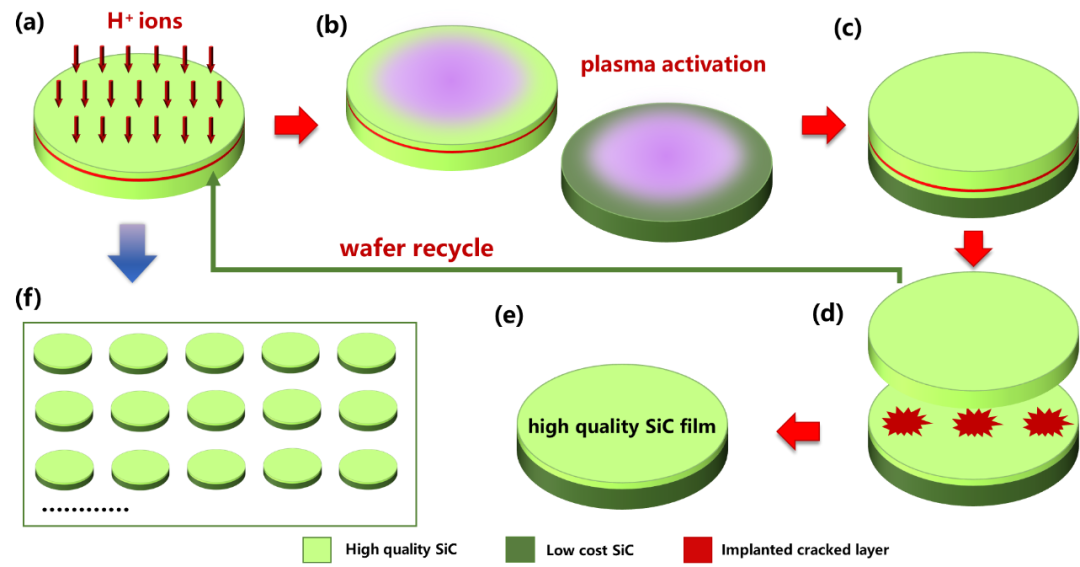

异质集成XOI课题组基于“万能离子刀”技术实现了SiC复合衬底的制备。如图1所示为复合衬底的制备工艺流程,首先对高质量SiC进行离子注入,而后经过表面处理后与低成本SiC键合在一起,经过退火剥离后将高质量SiC薄膜与SiC衬底结合在一起。通过回收剥离后的高质量SiC反复利用,实现单片SiC成本的大幅下降。目前技术水平预期可以将SiC晶圆回收循环利用10次,预期将使8英寸单片制造成本降低40%,提高回收技术水平将使单片成本进一步降低。

(a)离子注入;(b)表面活化处理;(c)键合过程;(d)退火剥离及晶圆回收;(e)最终优化后处理;(f)单片高质量SiC产出多片复合衬底晶圆。

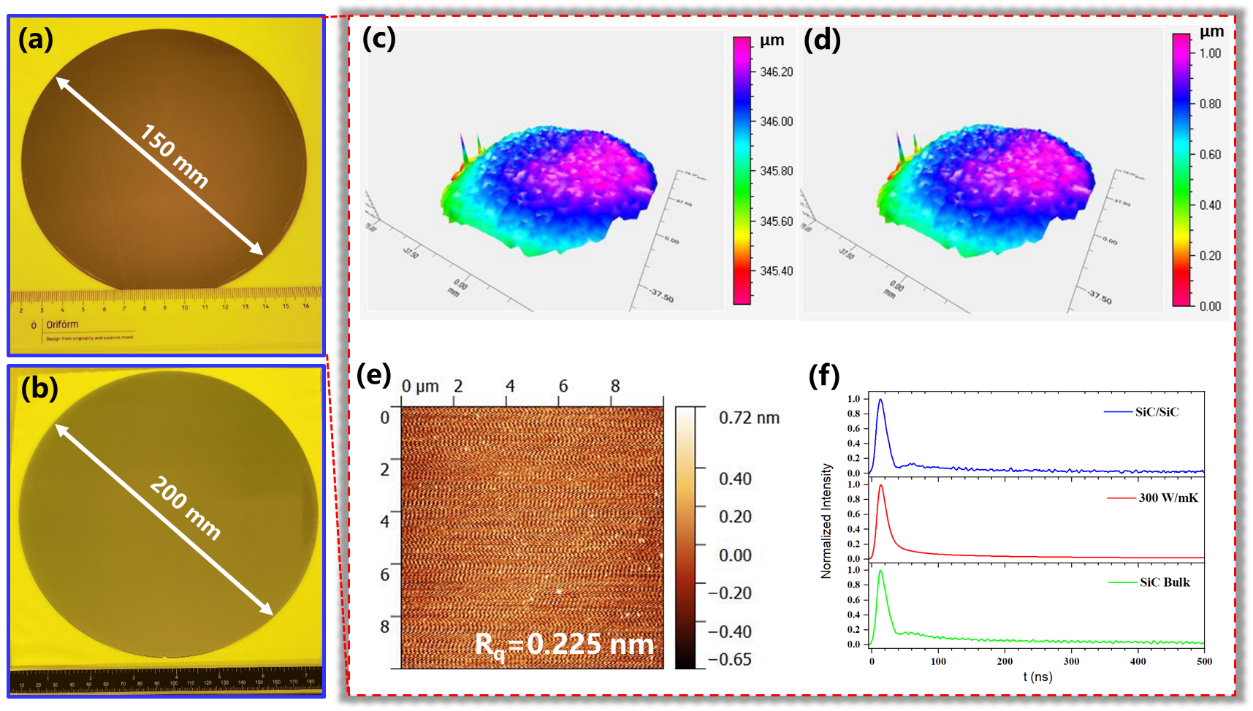

基于以上制备流程,团队实现了6英寸及8英寸的SiC复合衬底的制备,如图2(a、b)所示,制备的SiC复合晶圆厚度平均值346 μm,TTV为1.075 μm,Bow为8.429 μm,LTV为0.885 μm,表面粗糙度Rq为0.225 nm,基本达到后续外延需求。经过瞬态热反射热阻测试,拟合计算界面热阻约为0.01 m2K/GW,即键合界面附近热阻与体材料基本相当。

(a)150 mm SiC复合衬底;(b)200 mm SiC复合衬底;(c)衬底厚度(150 mm);(d)衬底TTV(150 mm);(e)表面粗糙度Rq(150 mm);(f)界面热阻测试(150 mm)。

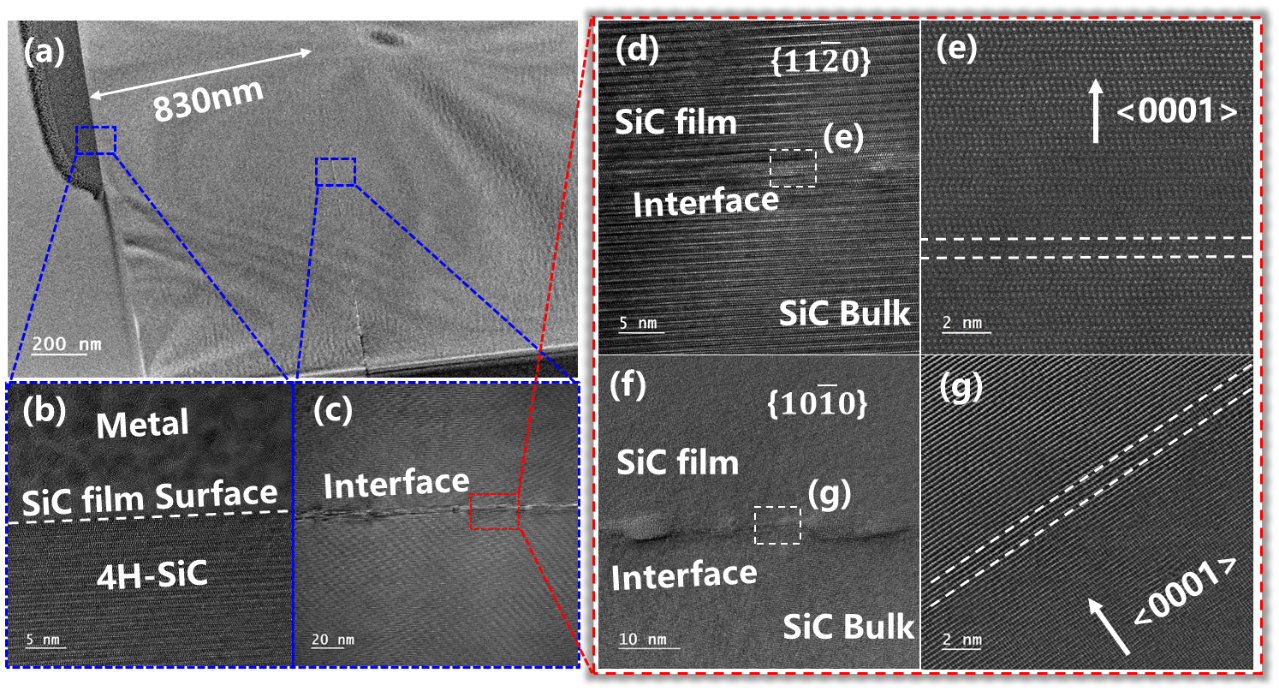

图3展示了复合衬底的微观TEM截面情况。经过对直接键合过程的技术优化,可以看到,虽然在低分辨率下可以看出键合界面,但是从暗场STEM测试结果来看,键合界面并没有明显的多晶区域,薄膜与衬底是以较好单晶状态结合在一起,这为纵向器件的载流子输运提供了良好基础。

图3 SiC复合衬底TEM截面图

(a)SiC复合衬底TEM截面;(b)样品表面区域;(c)键合界面区域;(d){

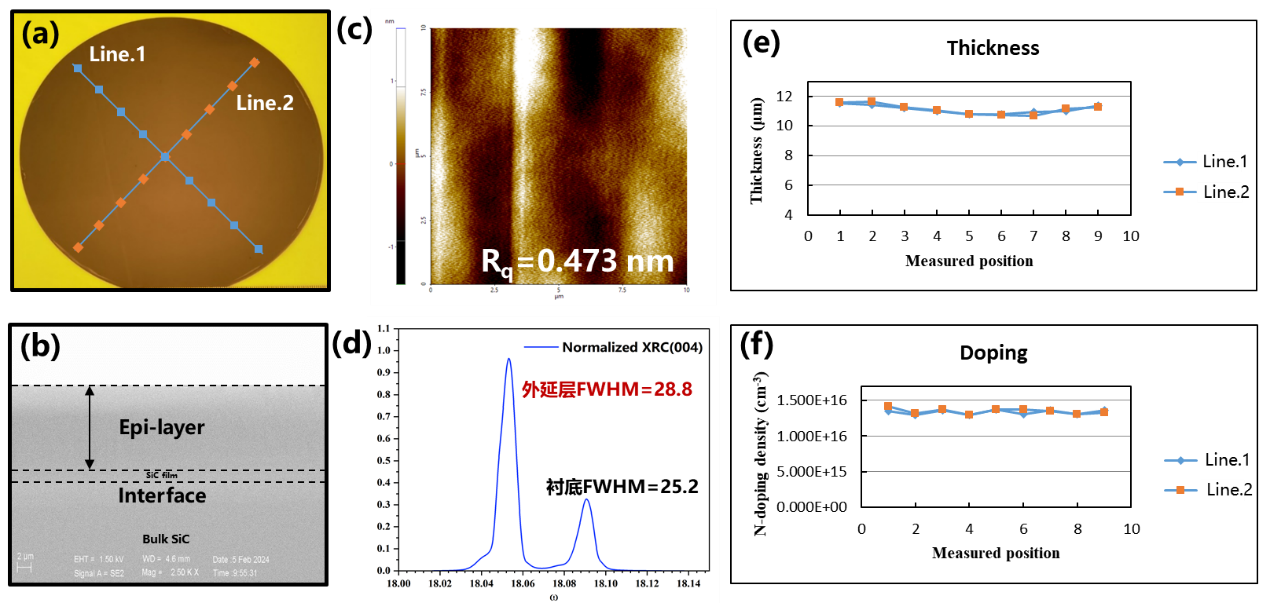

团队进一步对SiC复合衬底进行了外延验证,如图4所示。外延层表面粗糙度Rq为0.473 nm。由于外延SiC晶格匹配决定于转移的顶层SiC薄膜,而与支撑衬底存在一定失配,因此在XRC测试中存在两个高质量单晶峰。外延层厚度11.137 μm,面内厚度均匀性2.7%;载流子浓度1.34×1016 cm-3,面内载流子均匀度2.63%。总体上,SiC复合衬底可以支撑较高质量的同质外延生长。

(a)(e、f)图测试点位示意图;(b)外延结构SEM截面;(c)外延表面粗糙度Rq;(d)外延结构(004)面XRD摇摆曲线;(e)外延层厚度;(f)外延层载流子掺杂浓度。

未来XOI团队将进一步致力于高品质、低成本、大尺寸SiC异质集成技术的研究,为解决目前SiC的产业瓶颈提供可行方案。

联系方式:alyi@mail.sim.ac.cn

参考文献

Yi, A. et al. Silicon carbide for integrated photonics. Applied Physics Reviews 9, doi:10.1063/5.0079649 (2022).

Yan, F.-F. et al. Room-temperature coherent control of implanted defect spins in silicon carbide. npj Quantum Information6, doi:10.1038/s41534-020-0270-8 (2020).

Yi, A. et al. Wafer-scale 4H-silicon carbide-on-insulator (4H–SiCOI) platform for nonlinear integrated optical devices. Opt. Mater.107, 109990, doi:10.1016/j.optmat.2020.109990 (2020).

Wang, C. et al. High-Q microresonators on 4H-silicon-carbide-on-insulator platform for nonlinear photonics. Light Sci Appl 10, 139, doi:10.1038/s41377-021-00584-9 (2021).

Lv, Y. et al. MEMS Thermocouple Sensor Based on 4H-Silicon-Carbide-On-Insulator (4H-SiCOI). IEEE Sens. J.22, 13930-13936, doi:10.1109/jsen.2022.3181046 (2022).

图1 SiC复合衬底制备流程图

图1 SiC复合衬底制备流程图

图2 SiC复合衬底及其各项性能

图2 SiC复合衬底及其各项性能

![]() } 面键合界面区域HRTEM;(e){

} 面键合界面区域HRTEM;(e){![]() } 面键合界面区域STEM;(f){

} 面键合界面区域STEM;(f){![]() } 面键合界面区域HRTEM;(g){

} 面键合界面区域HRTEM;(g){![]() } 面键合界面区域STEM。

} 面键合界面区域STEM。 图4 150mm SiC复合衬底外延结果表征

图4 150mm SiC复合衬底外延结果表征

| 上一篇:企商在线石景山智能算力... | 下一篇:重磅:首片8英寸蓝宝石... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk