解析适用于 SiC 栅极驱动的 PCB 布局方法

2021/6/17 19:37:49 材料来源:CREE科锐

在为任一高功率或高电压系统设计印刷电路板 (PCB) 布局时,栅极驱动电路特别容易受到寄生阻抗和信号的影响。对于 (SiC) 栅极驱动,更需认真关注细节,因为其电压和电流的转换速率通常比硅快得多。遵循指定 PCB 设计指南,可以帮助减少这些常见隐患并消除实验室或现场故障。

SiC 功率电路的优点和注意事项

SiC 功率电子器件的主要优点是开关频率高、导通损耗低、效率更高且热管理系统更简单。与硅基转换器相比,由于 SiC 功率系统具有这些优势,因此能够在要求高功率密度的应用(如太阳能逆变器、储能系统 (ESS)、不间断电源 (UPS) 和电动汽车)中优化性能。但是,由于高电压转换速率 (dv/dt) 和电流转换速率 (di/dt) 是 SiC 功率器件的固有特性,使其与硅基电路相比,这些电路对串扰、误导通、寄生谐振和电磁干扰 (EMI) 更为敏感。(图 1)。

将功率 MOSFET 并联时,设计人员必须更密切地注意如何最大限度降低这些影响,因为器件之间的电流分配不均会影响性能。例如,在开关瞬变过程中,在并联中增加一个器件会使 di/dt 倍增,从而可能导致更大的电压过冲。此外,任何寄生电感都可能产生与反馈机制耦合的谐振,从而只会使电流不平衡的情况变得更糟。在这种情况下,PCB 设计人员必须特别注意要降低寄生电感。

电路板寄生现象对 SiC 电路的负面影响

SiC 电路中的寄生电感和电容

首先,SiC MOSFET 具有理想的固有低寄生电容(CGD、CDS、CGS)。这种特性支持高开关频率,因此有助于实现高功率密度设计。但是,与这种好处如影随形的是,在布局中不可避免地容易受到寄生电感谐振影响的情况。寄生电感本身可存在于应用电路的栅极回路 (LGS) 和功率回路 (LDS) 以及共源极电感 (LCS) 之中。如之前所述,导致这些电感的因素包括走线长度很长,以及器件引线之间的电感。

栅极回路电感会增加栅极电压的振铃,这反过来又会增加导通延迟,并且在某些情况下,会导致 MOSFET 的漏极-源极电压发生振荡振铃。通常,应最大限度地减小栅极回路电感以避免 MOSFET 的误工作,但这种寄生电感的影响是三种主要寄生电感中最小的。

整个器件的过冲电压通常由功率回路电感(有时也称为开关回路电感)造成,而这会产生高开关损耗。共源极电感会在开关瞬变过程中产生对栅极驱动的电压反馈,抵消栅极电压的变化并减慢漏极电流,从而显著增加导通和关断时的开关损耗。[1] 此外,并联器件之间微小的寄生 LCS 不匹配情况也会在开关瞬变过程中造成电流不平衡,从而放大负栅电压反馈的影响。

设计 PCB 时,不可能完全消除所有寄生电感和电容。但是,一些常用技术可以帮助最大限度地减小这些电感和电容。

应对 SiC 栅极驱动布局方面的挑战

使功率曲线远离栅极回路

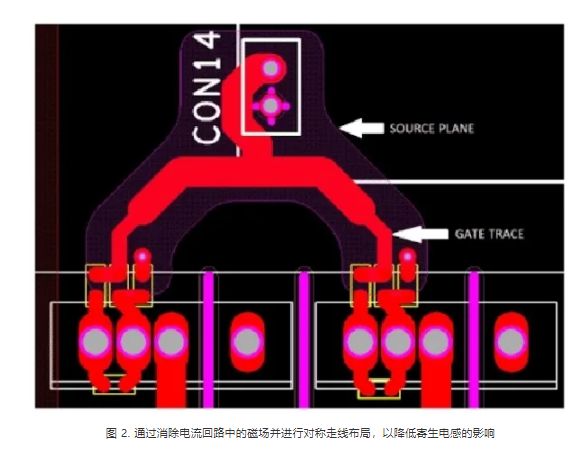

典型情况下,在单层 PCB 上布线的功率回路通常被称为“横向功率回路”。而第一个内层用作“屏蔽层”,以减少功率回路中高开关频率所产生的磁场的影响(图 2)。功率回路中的脉冲电流在屏蔽层内催生出电流和磁场,从而抵消功率回路中的电流和磁场。最终,由于有效地减小了功率回路和栅极驱动回路内包含的面积,这将降低寄生电感。

最大限度缩短栅极驱动和 MOSFET 之间的距离

任一栅极回路电感都会与输入电容产生谐振,并产生栅极-源极电压振荡,从而导致漏极-源极电压振铃。将栅极驱动放置在紧邻 SiC MOSFET 的位置,以最小的走线长度将栅极回路电感降至最低。此外,这种做法还有助于使各并联 MOSFET 设计之间的共源极电感保持恒定。

以最小走线长度使 PCB 布局保持对称

最大程度地缩短高频率栅极回路和功率回路的周长,以减少电压过冲和可能由该过冲引起的任何 EMI,是十分关键的。这对于并联器件尤其重要,因为寄生电感本来就更高。如图 2 所示,用于并联 MOSFET 的对称栅极驱动路径可实现更均匀的电流分布。

将小电容器置于栅极和源极之间

与硅基电路相同,通过在栅极和源极之间放置去耦电容器,可以最大限度地减少由瞬态信号引起的栅极电压尖峰。该电容为栅极驱动电流提供一个低阻抗路径,从而减小 VGS 的升幅。但这会减慢栅极驱动信号,从而增加开关损耗。因此,应调整 CGS 的值以平衡损耗和瞬态抗扰度。

增加 EMI 滤波器或缓冲器

可以通过增加 RC 缓冲器或铁氧体磁珠等组件来实现有效的 EMI 抑制。沿(漏极和源极之间的)DC 总线连接的 RC 缓冲器将吸收漏极处的寄生振铃或电压过冲。在高频率下,与栅极串联放置的高电阻、低电感铁氧体磁珠,可有效抑制栅极处的寄生谐振。此寄生振荡由漏极-源极电压瞬变引起,该瞬变在栅极电路上生成电压,有可能会在栅极引脚处的电容和寄生电感(LC 谐振腔)之间引起谐振。铁氧体磁珠可抑制这种振荡,而不会对开关性能产生负面影响。

对于基于 SiC 的布局需要额外注意的事项

SiC 基功率电子器件的布局方法在许多方面类似于硅基电路。在这些布局操作中要格外小心,才能最终解决快速开关功率器件的各类问题挑战,使得设计人员能够在其功率应用中充分利用 SiC 的所有优点。

参考资料

[1]. Z. Chen, D. Boroyevich and R. Burgos, "Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics," The 2010 International Power Electronics Conference - ECCE ASIA -, Sapporo, 2010, pp. 164-169, doi: 10.1109/IPEC.2010.5543851.

关于英文原稿,敬请点击【阅读原文】并选择“在浏览器打开”,或访问:

https://www.wolfspeed.com/knowledge-center/article/demystifying-pcb-layout-methodologies-for-sic-gate-drivers

更多技术文章、白皮书和在线研讨会信息,敬请访问【Wolfspeed Knowledge Center】:

https://www.wolfspeed.com/knowledge-center/

Wolfspeed SiC 功率半导体夏季系列在线研讨会将于 6 月 23 日-7 月 21 日的每周三举办,每场均有新议题精彩呈现。诚邀您的参加,现在就可通过以下链接, 进行会议注册:

| 上一篇:Sivers、Imec 和 ASM A... | 下一篇:科锐携手高斯宝,为服务... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk