先进封装之于 ――大有用武之地

2024/5/29 17:46:01 材料来源:ACT

作者:宗蕾,阮文彪,李金喜,厦门云天半导体科技有限公司

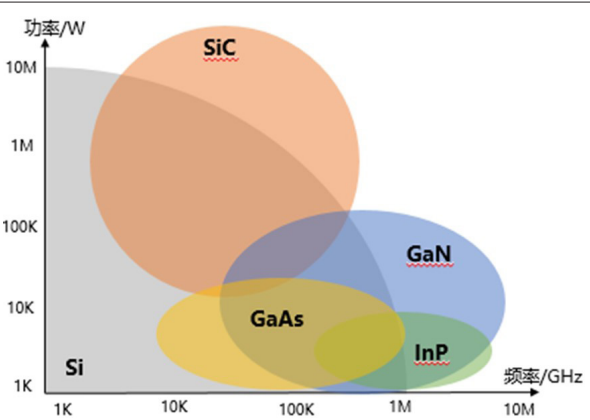

半导体材料的演进已历经三代,第一代的硅(Si)、锗(Ge);第二代的砷化镓(GaAs)、磷化铟(InP);第三代的

(SiC)、氮化镓(GaN)。目前,全球95%以上的集成电路(IC)是基于硅晶圆生产的。随着物联网、新能源汽车及5G时代的到来,以第二代和第三代半导体为代表的

正逐步渗透更多应用场景,市场规模也在不断扩大。

本文将结合不同半导体材料,特别是

的特性,阐述近年来呈爆炸式向各个方向发展的先进封装,在

器件制造中的应用。

为什么需要

?

虽然硅技术和产业链很成熟,芯片制造成本也低,但材料的物理性质限制了其在光电子、高频高功率器件和高温器件中的应用。三代半导体材料有着不同的特性,这也决定了它们自身的优势适合不同的应用场景。

第一代半导体包括硅、锗,其间接带隙较窄,饱和电子迁移率较低,主要应用于低压、低频(约3GHz)、中低功率(100W左右)的晶体管和探测器中,是目前半导体器件和集成电路的主要制造材料;由于产业链成熟、成本较低,渗透率已近95%。

第二代半导体包括砷化镓、磷化铟等,为直接带隙,电子迁移率更高,广泛应用于功率在100W左右、频率约100GHz的卫星通信、移动通信和GPS导航领域。不过,砷化镓资源较为稀缺,价格昂贵,且材料具有毒性,对环境危害较大,其渗透率近1%。

第三代半导体包括

、氮化镓等,具有禁带宽度大、击穿电场高、热导率高、电子饱和速率快、抗辐射能力强是优点,可满足电力电子技术对高温、高功率、高压、高频以及抗辐射等工作场景的要求,其渗透率近5%。

事实上,随着硅半导体材料主导的摩尔定律逐渐走向其物理极限,具有高电子迁移率、高临界击穿场强、高导热能力以及直接能隙与宽能带等特性优势的

开始崛起,有望成为超越摩尔定律的途径之一。图1是第二代和第三代半导体的

的应用分类。

值得一提的是,随着

器件的日益普及和广泛应用,出于应用需求,对

器件和模块的封装也提出了新的要求,如低损耗、低感量、高功率密度、高散热性能、高集成度、多功能等,正催生出与硅器件封装技术和产品形式不同的发展路线,目的是利用先进封装工艺满足上述要求,同时提升产品的可靠性。

的先进封装

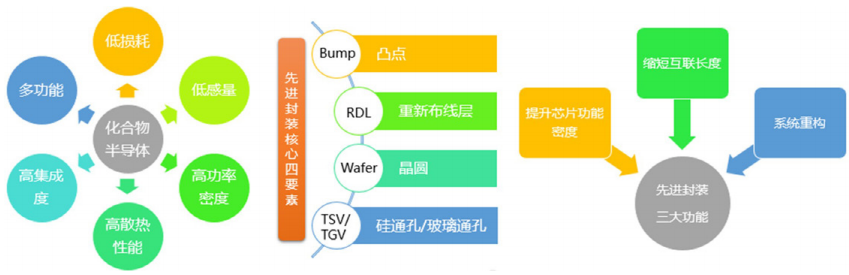

事实上,先进封装的发展起源于业界头部代工厂,例如,近年来,英特尔在先进工艺的研发方面频频“难产”,逐渐与台积电、三星拉开了差距。因此,英特尔愈发看重先进封装的研发,不断发力先进封装技术。相比传统封装,通过采用先进设计理念和先进集成化加工工艺,先进封装有助于提升芯片功能密度、缩短互连距离和实现系统重构。

现阶段,先进封装类别主要包括倒装焊(Flip-Chip)、晶圆级封装(WLP)、2.5D封装(Interposer(中介层))、3D封装(TSV/TGV/Embedded)、系统级封装(SiP)、小芯片(Chiplet)等。图2显示了先进封装的的要素和功能。

功率电子应用

的封装

几经迭代,功率半导体正在向低阻抗、高功率、高频率特性演变。高功率密度、小尺寸的特性使得GaN和SiC成为功率半导体的新宠,GaN功率电子器件主要以高电子迁移率晶体管(HEMT)为主,在高频功率应用方面有巨大潜力;而SiC功率器件主要是二极管(SBD/JBS)和金属-氧化物半导体场效晶体管(MOSFET),适用于功率在1kW-500kW、工作频率在10kHz-100MHz的场景。两者都可应用于对能量效率和空间尺寸要求较高的应用。

需要指出的是,要充分发挥

材料的优异特性给封装技术带来了一些新的挑战,封装在很大程度上决定了功率半导体器件是否具有更高的功率密度和可靠性,是否能耐受更高的温度,更好地适应恶劣环境。

传统硅基功率器件封装普遍采用引线键合和单面散热技术,存在寄生参数较高、散热效率差的问题。为解决这些问题,无引线互连和双面散热等技术应运而生。

GaN HEMT器件封装路线

GaN HEMT器件封装路线技术发展路线图及先进封装应用实例如图3所示。可以看到,伴随看高频率的升高和功率密度的增加,键合材料和封装方式都在变化,以适应GaN HEMT器件性能的逐步提升。

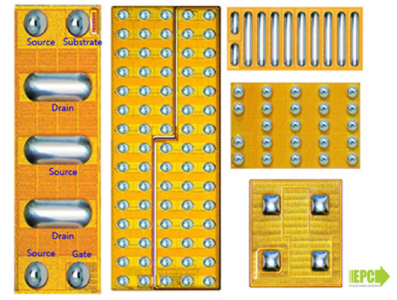

一个应用实例是EPC公司的晶圆级CSP封装方法,为了优化开关性能,最大限度减小封装寄生效应,它采用在钝化芯片的源极、栅极及漏极上形成Bump(凸点),将其直接贴装在PCB上。由于没有键合线,最大限度减小了寄生电感和界面热阻,见图4。

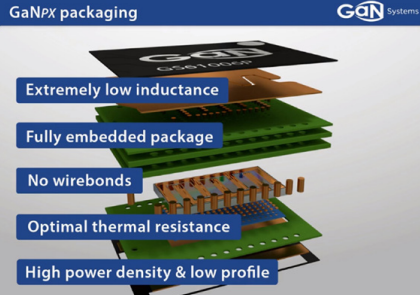

另一个应用实例是GaN Systems的定制化嵌入式封装解决方案,采用了独有的专利技术Island Technology,实现大电流芯片性能和良率,同时用GaNPX®封装技术实现小型封装中的低电感和低热阻,见图5。

SiC MOSFET新封装结构

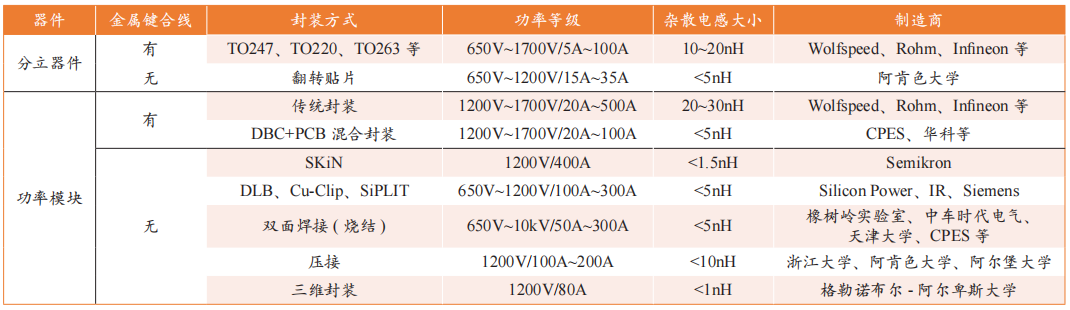

SiC器件的结电容更小,栅极电荷更低,因此开关速度极快。由于开关过程中电压和电流随时间的变化率(dv/dt和di/dt)极高,会出现驱动电压波形过冲和震荡,增加器件电压应力、开关损耗及电磁干扰问题,严重时甚至引起功率器件误开关,因此,SiC功率器件对寄生电容和寄生电感更加敏感。针对上述问题,国内外同行开发了一系列新的封装结构,用于减小杂散参数,特别是杂散电感,如表1所示。

表1:SiC器件典型封装结构(中国电机工程学报)

以下分别介绍三类SiC MOSFET的封装形式。

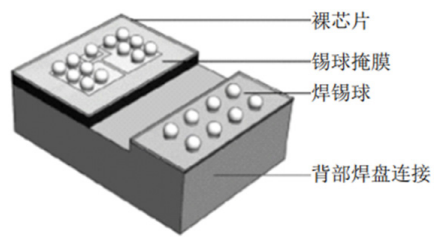

(1)单管翻转贴片封装

阿肯色大学团队借鉴BGA封装技术,提出了一种单管翻转贴片封装技术,见图6。方法是通过一个金属连接件将芯片背部电极翻转到和正面电极相同的平面位置,然后在相应电极位置上植上焊球,以此消除了金属键合线和引脚端子。相比TO-247封装,其体积减小了14倍,导通电阻减小了24%。

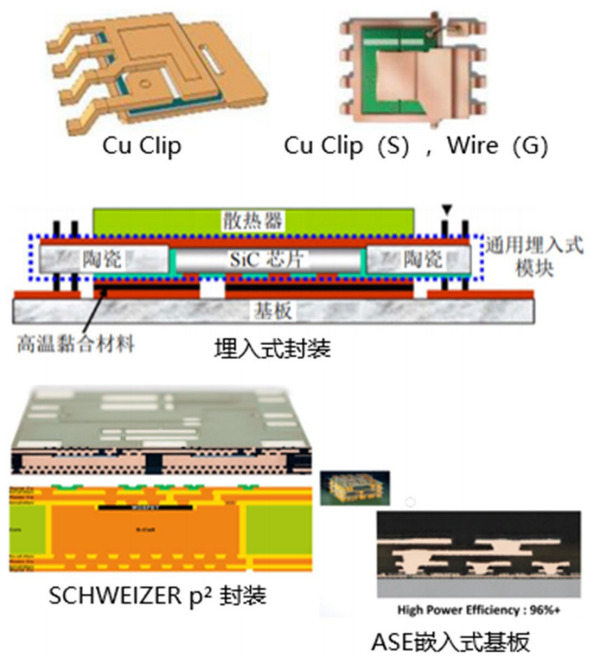

(2)芯片正面平面互连封装

平面互连方式不仅可以减小电流回路,进而减小杂散电感和电阻,还具有更出色的温度循环特性和可靠性。

①Cu-Clip(铜夹片):是一种新型芯片互连技术,利用特殊的铜夹片实现芯片与封装基板的连接,需要采用溅射及电镀或化镀工艺实现芯片表面的金属化处理;

②嵌入式:该方法将芯片置于陶瓷定位槽中,再用绝缘介质填充缝隙,最后覆盖掩膜两面溅射金属铜,以实现电极连接。通过选择合理的封装材料可以减小模块在高温时的层间热应力,并能在279℃的高温下测量模块的正反向特性。平面直连封装工艺通过消除金属键合线,将电流回路从DBC板平面布局拓展到芯片上下平面的层间布局,显著减小了回路面积,还可实现低杂散电感参数。例如SCHWEIZER公司的p²封装和ASE的嵌入式基板都是将功率半导体嵌入印制电路板的技术,如图7所示。

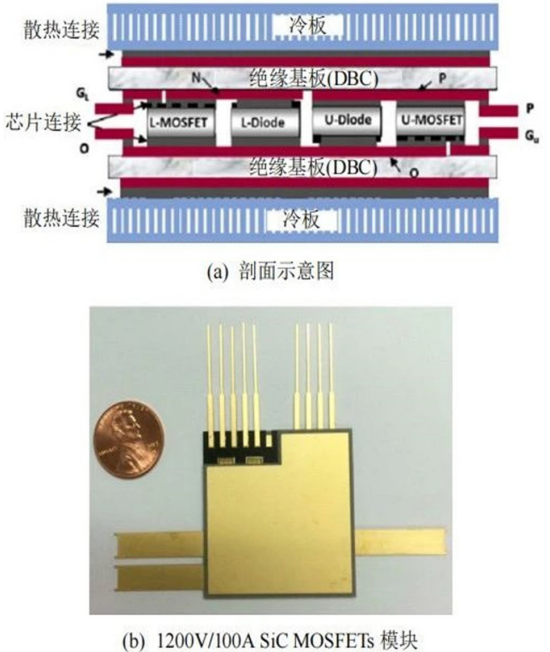

(3)双面散热封装技术

图8是一个典型双面散热封装SiC模块,其上下表面均采用DBC板焊接,可实现上下表面同时散热。该工艺的难点在于,芯片上表面需要进行溅射或电镀处理使其可焊接,且在芯片上表面还要增加金属垫片、连接柱等,以消除同一模块中不同芯片的高度差。由于SiC芯片面积普遍很小,如何保证在有限的上表面面积范围内的焊接质量是该工艺的关键。得益于上下DBC的对称布线与合理的芯片布局,该封装可将回路寄生电感参数降到3nH以下,相比传统封装模,块热阻可下降38%。

光电子应用

的封装

目前,光电子器件及组件与IC或I/O外引线的连接主要基于陶瓷板载芯片共晶焊,或采用胶结以及金丝球键合。模块封装采用传统的SMD封装,即将光器件或组件与PCB电互连,然后根据协议或客户指定的外壳实现封装工艺。

(1)Mini/MicroLED封装

Mini/MicroLED主要采用直显封装,如IMD/COB技术,背光封装多采用COB/COG技术;

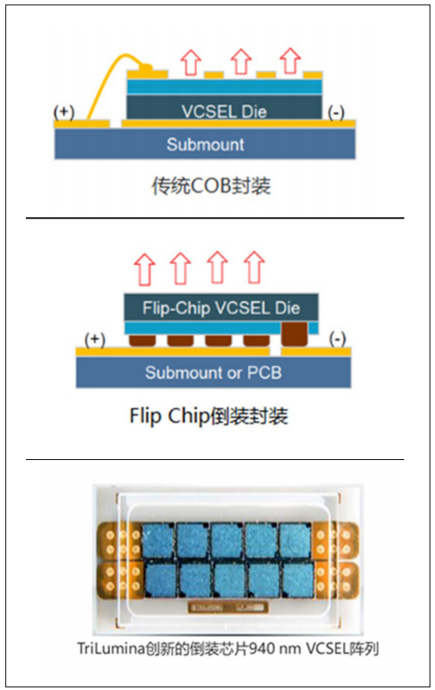

(2)VCSEL激光器封装

传统VCSEL采用COB封装。为了降低杂散电感,衍生出了FlipChip封装,其优点包括:减少封装步骤、降低封装成本、低电感,实现2D阵列可寻址、晶圆级光学集成等。图9是几种VCSEL激光器封装形式。

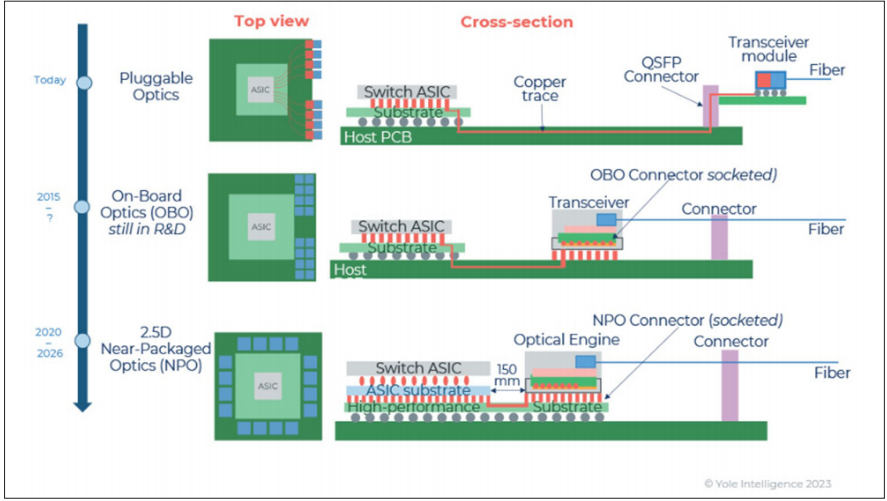

(3)光模块光电合封

光电合封解决了小尺寸可插拔光学收发器带来的一些挑战,如热管理、功耗、带宽和端口密度,如图10所示。其目的是使电光转换过程尽可能靠近计算、转换或ASIC,以获得更高的带宽和能量效率。将有源器件和光收发器安装在同一基板上,可以消除主板上铜线路造成的所有损耗和失真。

2.5D/3D封装难点在于高密度光电载板工艺、高精度的光电芯片组装工艺,以及阵列光纤连接器的耐高温性。

射频通信应用

的封装

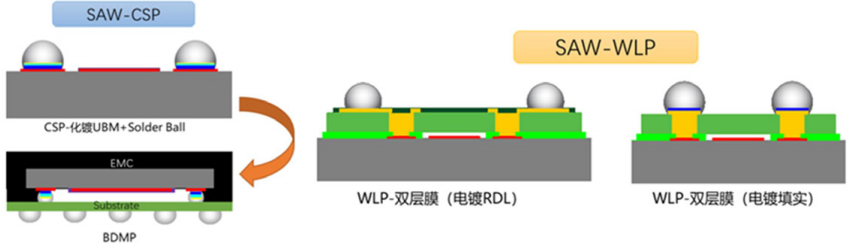

射频前端器件的工艺技术分类如图11所示,目前RF SAW滤波器常用的两种封装结构分别为BDMP和WLP。在射频前端器件工艺技术中,RF开关的工艺包括CMOS、硅、砷化镓、氮化镓;RF滤波器采用BAW和SAW工艺;高功率放大器的工艺有砷化镓和氮化镓;放大器工艺主要是氮化镓、氮化镓、SOI、硅锗和硅。

云天半导体的先进封装

厦门云天半导体科技有限公司(简称云天半导体)成立于2018年7月,致力于高速、高频通信等应用的先进封装与系统集成,通过自主研发与持续创新,为客户提供从产品协同设计、工艺研发到批量生产的全流程解决方案和服务。

云天半导体一期厂房建筑面积约为4500平米,引入国内稀缺的4/6英寸晶圆级3D封装平台,特别针对SAW/FBAR等产品应用;二期厂房建筑面积约为35000平米,已于2022年9月通线,引入4/6/8/12英寸晶圆级封装平台,总体规划产能8万片/月,目前释放产能1万片/月,主要聚焦IPD/WLCSP/FO等封装。

云天半导体的“特色工艺+先进封装”主营业务涵盖以下四大板块:

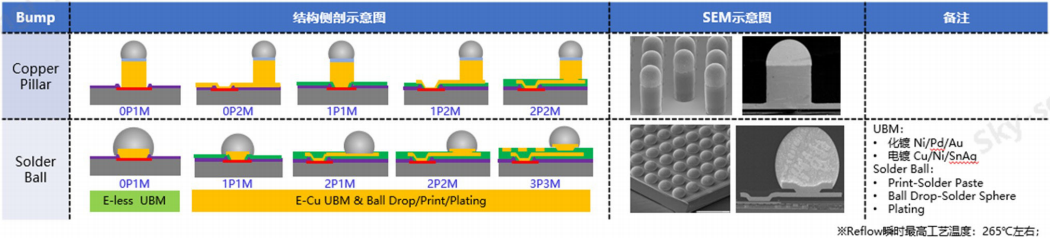

(1)WLCSP/Bumping(凸点制作)

云天半导体提供0P1M、1P1M、2P2M、3P3M等SolderBall及CopperPillar工艺,见图12。三种成熟的SolderBall实现工艺包括:Print(钢网印刷)、Balldrop(植球)和Plating(电镀)。工艺能力包括化镀NiAu/NiPdAu以及电镀Cu/Ni/SnAg。针对SAW和FBAR产品,具备成熟的CSP封装工艺(化镀UBM+BGA)以及WLP双层膜工艺(电镀RDL结构和电镀填实结构)。

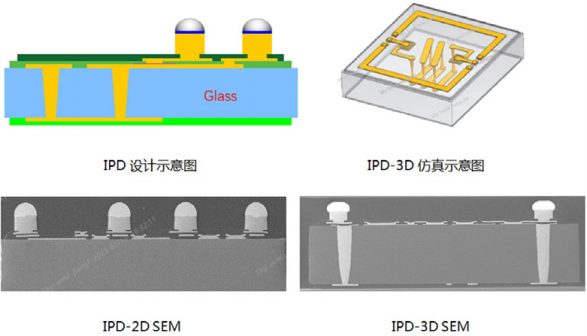

(2)IPD

图13是颇具特色的晶圆级玻璃基IPD产品,它具有低成本、高集成度、高Q值等特性,适用于高频应用领域。根据不同电感设计方式,IPD可分为2D结构(平面电感)和3D结构(3D电感)。

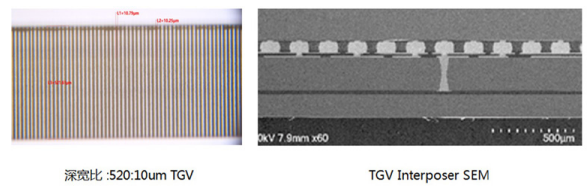

(3)Interposer(中介层)

图14是云天特色的2.5D玻璃中介层产品,它采用激光诱导+刻蚀方式形成玻璃通孔,具备大规模量产能力,同时配备玻璃通孔及玻璃表面金属化能力,有助于实现信号互连。该产品具有优良的高频电学、机械特性,而且成本低、工艺流程简单,广泛应用于射频组件、光电集成、MEMS等领域。

(4)SiP

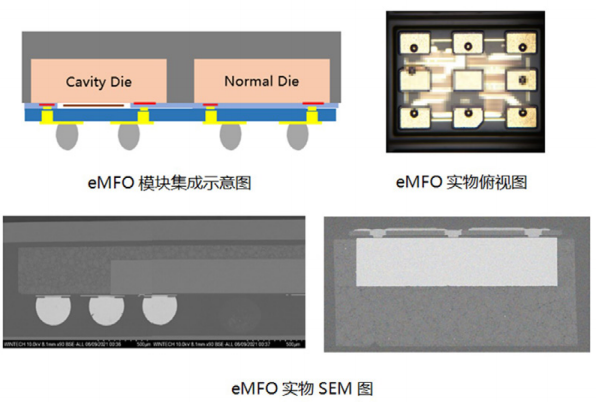

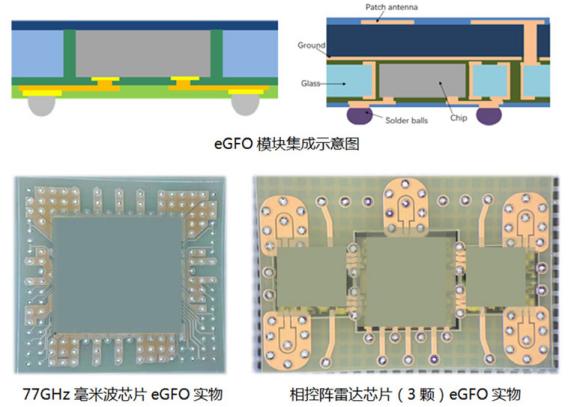

云天半导体的SiP封装主要基于新型晶圆级扇出工艺,根据芯片埋入基底材料不同,分为塑封料扇出封装(eMFO)和玻璃基扇出封装(eGFO)两大类。

①eMFO:用于射频器件模块集成,具有高可靠性、多芯片集成的特点;用于光收发芯片集成,具有性能优异、易于批量生产的特点,见图15。

②eGFO:是适用于高频领域理想的系统集成解决方案,具有低成本、低损耗、可扩展到方板、以及优良的电学特性及机械性能,可以通过TGV集成天线3D封装(AiP),见图16。

除了以上四大全流程业务板块外,云天半导体还可承接以下短流程工艺,满足客户的不时之需:

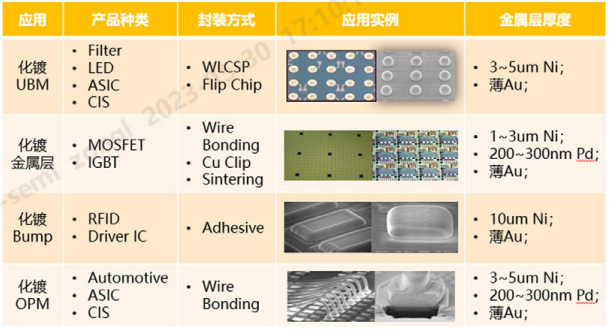

化镀镍金或镍钯金应用涵盖化镀UBM、化镀金属层、化镀Bump、化镀OPM等,见图17/图18。

化镀工艺能力支持晶圆尺寸、晶圆衬底、Pad形状、最小化镀Pad、阶梯化镀深度、最薄化镀金属层、来料厚度、化镀厚度范围和Passivation等,如表2所示。

表2:化镀工艺能力。

③DPS(CP测试/研磨&切割/分选编带)

DPS的工艺流程包括:分选→切割→晶圆测试→研磨。CP测试设备构架如图19所示。

△ 图19:CP测试设备构架。(图源:云天半导体)

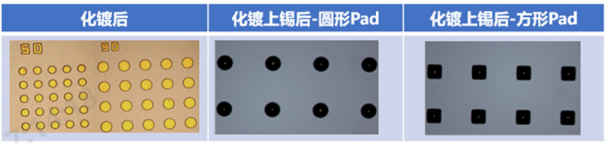

如表3所示,DPS的研磨工艺适用于单一材质和混合材质,具备不同的量产能力和工程样品能力。DPS切割工艺目前主要采用机械切割和激光隐切两种,支持各种晶圆材质。

表3:DPS研磨和切割工艺。(图源:云天半导体)

DPS分选编带设备有两种,均支持4、6、8英寸晶圆,表4给出了具体工艺能力参数。

表4:DPS分选编带设备参数。(图源:云天半导体)

总结

今天,集成电路技术已进入“后摩尔时代”,受成本及技术壁垒等因素的限制,先进制程短期内突破难度很大,而通过先进封装提升芯片整体性能并有效降低成本,已成为集成电路产业发展的热门赛道。

厦门云天半导体在先进封测领域深耕多年,具备从4寸、6寸、8寸到12寸全系列晶圆级封装工艺能力,以WLCSP/IPD/TGV/Fan-out等领先创新技术为客户提供系统封装集成解决方案和量产服务。针对化合物导体材料的成熟的WLCSP/Bumping和FO先进封装技术可以实现全流程的Turnkey交付。未来,云天团队将继续发扬“创新、卓越、合作、奋斗”的精神,不断创新,挑战极限,为客户提供更具性价比的解决方案。

△ 图1:

的应用分类。(图源:英飞凌)

△ 图1:

的应用分类。(图源:英飞凌) △ 图2:先进封装的要素和功能。

△ 图2:先进封装的要素和功能。 △ 图3:GaN HEMT器件封装路线图。(图源:电子与封装)

△ 图3:GaN HEMT器件封装路线图。(图源:电子与封装) △ 图4:晶圆级CSP封装。(图源:EPC)

△ 图4:晶圆级CSP封装。(图源:EPC) △ 图5:定制化嵌入式封装。(图源:GaN Systems)

△ 图5:定制化嵌入式封装。(图源:GaN Systems)

△ 图6:单管翻转贴片封装。(图源:University of Arkansas)

△ 图6:单管翻转贴片封装。(图源:University of Arkansas) △ 图7:嵌入式基板封装。(图源:SCHWEIZER和ASE)

△ 图7:嵌入式基板封装。(图源:SCHWEIZER和ASE) △ 图8:典型双面散热封装SiC模块。(图源:中国电机工程学报)

△ 图8:典型双面散热封装SiC模块。(图源:中国电机工程学报) △ 图9:VCSEL激光器封装。(图源:AMS-Osram和TriLumina)

△ 图9:VCSEL激光器封装。(图源:AMS-Osram和TriLumina) △ 图10:光电合封截面图。(图源:Yole Group)

△ 图10:光电合封截面图。(图源:Yole Group) △ 图11:射频前端器件工艺技术分类。(图源:云天半导体)

△ 图11:射频前端器件工艺技术分类。(图源:云天半导体) △ 图12:SolderBall及CopperPillar工艺。(图源:云天半导体)

△ 图12:SolderBall及CopperPillar工艺。(图源:云天半导体) △ 图13:晶圆级玻璃基IPD产品。(图源:云天半导体)

△ 图13:晶圆级玻璃基IPD产品。(图源:云天半导体) △ 图14:2.5D玻璃中介层。(图源:云天半导体)

△ 图14:2.5D玻璃中介层。(图源:云天半导体) △ 图15:eMFO。(图源:云天半导体)

△ 图15:eMFO。(图源:云天半导体) △ 图16:eGFO。(图源:云天半导体)

△ 图16:eGFO。(图源:云天半导体) △ 图17:化镀应用。(图源:云天半导体)

△ 图17:化镀应用。(图源:云天半导体) △ 图18:化镀TestVehicle实物效果图。(图源:云天半导体)

△ 图18:化镀TestVehicle实物效果图。(图源:云天半导体)

| 上一篇:β-Ga2O3器件的液体雾化... | 下一篇:为什么CMOS 2.0是摩尔定... |