辉煌的栅极氧化物

2023/12/25 10:00:30 材料来源:ACT

人们是否应该担心负栅压应力下 SiC 功率 MOSFET 的栅极氧化物的寿命?绝对不,现在实验表明,它们与在正栅极应力下的寿命一样长

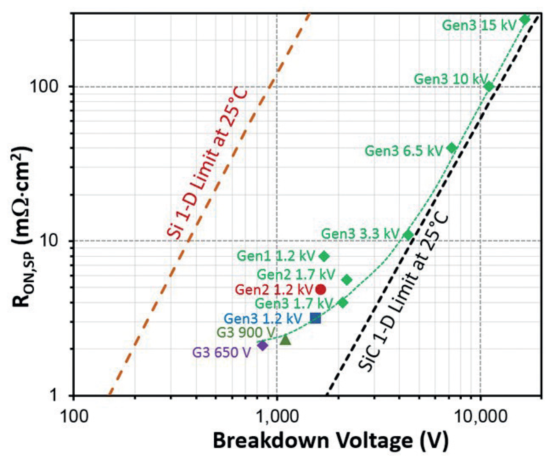

4H-SiC 的最大优势之一是击穿电场约为硅的十倍。这意味着,在给定的额定电压下,SiC功率器件可以具有比硅器件更薄的漂移区和更高的掺杂。反过来,这使得SiC功率器件具有更低的导通电阻(参见图 1)和简单的单极 MOSFET 结构——不需要复杂的结构,包括超级结或双极传导。最重要的是,SiC功率器件在相对较高的温度下具有较低的漏电流和较高的导热性,它支持通过低导通电阻实现更高电流密度。

由于所有这些特性,SiC MOSFET 在功率密度、效率、开关速度和热管理方面表现出比其他材料系统的明显优势。这些优势如此明显,以至于如果地球上的每个数据中心都使用SiC而不是现有的硅,那么曼哈顿就可以通过这种宽带隙材料提供的能源节省来维持一整年的供电。

SiC功率器件的成功故事可以追溯到千禧年之后。其中一个关键的里程碑是在 2002 年,当时我们公司 Wolfspeed 发布了第一个商业化的 600V 结势垒肖特基二极管。2011 年,我们又推出了业界第一个额定电压为 1200V 的 SiC MOSFET;在接下来的三年内,我们又推出了全球第一个1700 V SiC半桥模块。

最近,我们在提高产能方面的努力一直占据着头条新闻。2022年4月,我们开设了世界上第一个 200 毫米 SiC 晶圆制造厂,预示着 SiC 功率器件电气化的现在和未来。

我们并不是唯一一家生产 SiC 功率器件的公司,这些器件正在汽车、可再生能源、电源和工业应用中得到应用。让我们在同行中脱颖而出的是最广泛的商业产品组合,目前包括采用分立封装和裸片形式的 SiC MOSFET 和肖特基二极管,以及功率模块。我们的 SiC MOSFET 的电压范围为 650V至1700V,导通电阻范围为 10-1000 mΩ;我们的肖特基二极管系列的电压范围为 600 V至1700 V,具有同类产品最佳的正向压降,可减少传导损耗并提高整体系统效率。我们将继续进行多样化发展,最近推出了紧凑型QFN 8 mm×8 mm封装中的650V肖特基二极管,以及采用 TO无引线封装的 650V MOSFET,其面积比目前市场上的通孔封装小60% . 另一项突破是推出了我们的E系列功率器件:它们经过了湿度耐受强的汽车认证,并针对车载充电器、DC/DC 转换器和动力传动系统应用以及光伏逆变器进行了优化。此次发布进一步提升了我们在汽车市场领域SiC 器件的声誉。

评估可靠性

由于SiC 衬底质量、外延生长能力和器件加工的不断进步,SiC功率器件的可靠性水平已经很高,并且处于上升趋势。然而,苛刻的操作条件,加上不断变化的市场需求,使得对SiC功率器件的栅氧化物可靠性要求越来越高。

栅氧化物的可靠性有两个关键方面:阈值电压稳定性和栅氧化物寿命。诺贝尔奖获得者物理学家赫伯特·克罗默 (Herbert Kroemer) 曾说过一句著名的话:“界面就是器件”,这句话是正确的。由于SiC和硅MOS界面之间的差异,SiC栅氧化物的可靠性一直被仔细审查,并与硅器件的栅氧化物可靠性进行比较。

通常,SiC MOSFET的阈值电压稳定性与硅同类产品的阈值电压稳定度相似。但是,这两种材料系统之间存在着根本性差异。这些差异包括与硅和SiO2相比,4H-SiC和SiO2间的导带和价带偏移较小;4H-SiC MOS器件的界面陷阱密度较高;以及界面化学的差异—SiC 采用氮化栅极氧化物,SiO2/硅界面采用氢钝化。由于所有这些差异,SiC 和硅 MOS 器件之间的阈值电压偏移机制可能不同。

在宽带隙领域,人们投入了大量精力,通过偏置温度不稳定性测试来揭示所观察到的 SiC MOSFET 阈值电压变化背后的机制。这些研究考虑了正负栅极偏置,并证明了阈值稳定性以及实际应用的长期可靠性。

对 SiC MOS 器件,栅极氧化物可靠性的第二部分,即栅极氧化物寿命,也进行了仔细研究。我们公司通过恒定和斜坡式正栅极偏置时间依赖的介电击穿研究,报告了n沟道SiC功率MOSFET在175℃和大约4 MV/cm的栅极氧化电场下,具有吸引力的栅极氧化物失效时间中值为10000年。

对于硅 MOSFET,时间依赖性介质击穿可以说是有史以来特征最明显、被引用最多的失效机制之一。尽管存在多种模型,但对于 SiC,大多数研究人员使用线性热化学电场模型来解释随时间变化的介电击穿。这往往会提供最保守的估计。在两种更常见的替代方案中,考虑电场反比的模型给出了极其乐观的固有寿命推断,因此其有效性值得怀疑;而基于电压控制的幂律模型是不合适的,因为它是为超薄栅极氧化物开发的。由于这些问题,线性电场模型被广泛用于 SiC 也就不足为奇了。该模型假设正栅极电压会导致载流子隧穿,从而在氧化膜中产生缺陷。当这些缺陷达到临界点时,它们会在该局部薄弱点引发介电击穿。

评估负偏压

好奇的读者可能已经注意到,虽然 SiC 社群对阈值电压稳定性的讨论包括正负栅极偏压,但在谈到栅极氧化物寿命时,主要是 n沟道 SiC MOSFET 的正栅极偏置应力。出现这种情况是因为,直到我们最近的研究,几乎没有发表的关于 SiC MOSFET 在负栅极偏压下的栅极氧化物寿命的相关研究。这无疑是一个重大的遗漏,因为要关闭这些增强型 n 沟道器件,需要通过使栅极偏置远低于栅极阈值电压并至少降至 0 V 来关闭沟道。从阻断的角度来看,器件在 0 V 栅极偏压下轻松实现这一点没有问题。然而,在关断期间,通过施加远低于 0 V 的栅极偏压可以提高器件性能。使用负栅极偏压关断 MOSFET,通过在关断瞬变期间增加栅极电流来减少关断能量损失 - 反过来,这迫使栅极电容比使用 0 V 偏压关闭时放电更快。需要考虑的另一点是,在采用多个器件并联或桥接配置的系统中,器件往往以负栅极偏压关闭。采用这种方法是因为它提供了对寄生关断的进一步保护,寄生关断可能在系统中多个芯片之间的不平衡瞬变时发生。由于负栅极偏压的重要性,以及随后在这种偏压条件下对 SiC 功率器件的栅极氧化物寿命进行研究的必要性,当然需要对负栅极偏压进行迄今为止被忽视的仔细研究。

为了加深对SiC MOSFET在负栅极偏压下的栅极氧化物可靠性的理解,我们在 175℃下对我们的 Gen3 1200 V 分立式 MOSFET 进行了恒定电压时间依赖性介电击穿测试,施加的负栅极偏压远高于推荐的最大工作栅极电压 -4 V。将源极和漏极保持在地电位,我们在三个栅极应力电压下评估了大约 30 个器件,这三个栅极应力电压是:-29.5 V、-31 V 和 -32.5 V。我们分别监测了每个器件的栅极漏电流 ,这使我们能够在这些加速测试期间收集受压器件的单独失效时间。为了进行真正的比较,我们还使用与负偏压情况相同的样本大小,在Gen3 1200 V器件上进行了正栅偏压时间依赖介电击穿研究,其栅极应力电压为+29.5 V、+31 V和+32.5 V。

我们发现每种应力条件下的失效时间都遵循良好的 Weibull 分布。被称为 Weibull β特征提取值—它被称为形状参数,它代表故障率行为—远高于 2,表明在正负栅极应力下都有固有的老化故障机制。由于我们发现了相似的失效时间分布和 Weibull β值,因此我们可以得出结论,在正负栅极偏压下很可能存在相似的失效机制。

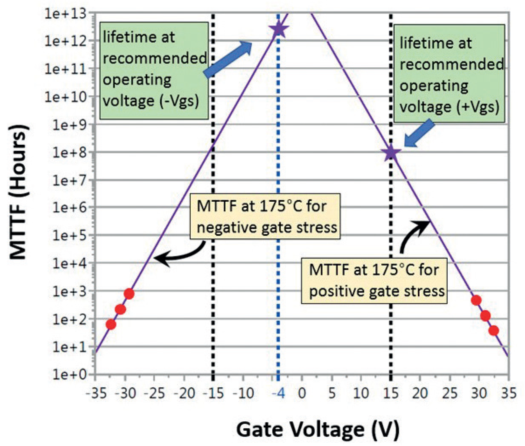

根据Weibull 失效时间分布、线性电场加速模型和最大似然估计,我们提取了失效的中位时间值并推断出寿命。我们发现,栅极氧化物的寿命在正负偏压下几乎是相同的,失效的中位时间约为10,000年(这是在175℃和-15/+15V的栅极应力条件下,对应于大约为 4 MV/cm 的栅极氧化物电场)。我们要指出的是,由于MOSFET关断沟道时推荐的负栅极源电压-4 V通常远低于导通状态期间的推荐正栅源电压+15 V,因此关断状态下的氧化物寿命应该比导通状态操作器件长得多(参见图2)。

在这一点上,虽然您可能对负栅极偏压下出色的 SiC MOSFET 栅极氧化物寿命印象深刻,但您可能想知道这一观察结果背后的物理解释是什么。让我们试着更详细地解释一下。正如我们已经提到的,隧道效应是栅极时间依赖性介电击穿的主要原因,一旦缺陷累积达到临界点就会发生击穿。因此,如果正负栅极偏压下的电流水平相似,那么在栅极氧化物中发生的损坏程度以及由此产生的栅极氧化物寿命也是如此。这种观点是可信的,因为电子在正栅极偏压下的能垒约为 2.8eV,而空穴在负栅极偏压下的能垒为 2.9eV。我们的 TCAD 模拟和电气测量进一步支持了这个观点。它们表明,在正负栅极偏压下,相似的势垒高度会导致相似水平的 Fowler-Nordheim 隧道电流的相似水平,从而解释了在这两种情况下栅极氧化物寿命的相似性。

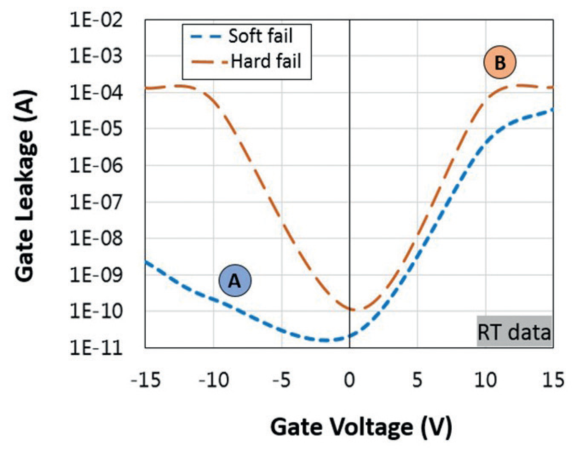

我们还建立了 MOSFET 元胞中的故障位置与时间依赖介质击穿应力期的故障特征之间的相关性。在所有三种应力电压(-29.5V,-31V,和-32.5V)下,负偏压下的时间依赖介电击穿应力的栅极泄漏曲线显示出两种不同的故障特征——软故障,“A”和硬故障,“B”。我们发现,“A”型器件中的故障后泄漏比“B”型故障器件中的泄漏低几个数量级。

作为这项研究的一部分,我们测量了具有不同原位漏电特征的故障器件在一定栅极电压范围内的室温栅极漏电流(见图 3)。当应用正栅极电压扫描时,我们发现 "A "型和 "B "型器件具有非常相似的高电流水平,在栅极电压为15V时超过10μA。但当我们用一系列负栅极电压扫描时,结果有明显的不同。我们称之为为“A”型的“软”故障器件表现出的电流比遇到硬故障的“B”型器件低几个数量级。这一观察结果与在时间依赖介电击穿应力期间在较高偏压和温度下记录的原位数据一致。

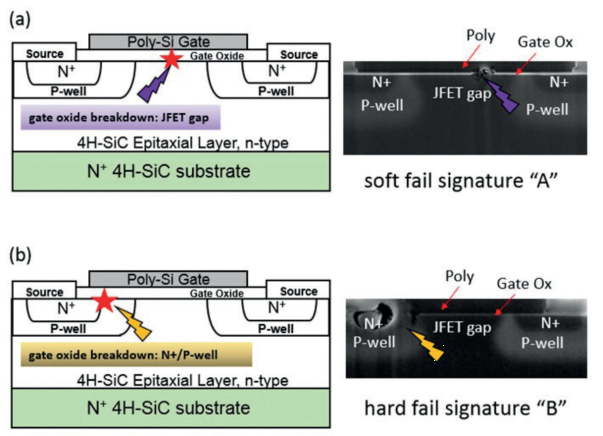

我们下一步是试图确定不同的电气故障特征——即“A”型和“B”型器件——是否与 MOSFET 元胞中的故障位置有任何程度的相关性。为了了解情况是否如此,我们进行了物理故障分析,包括热成像、聚焦离子束横截面和扫描电子显微镜成像。这些形式的显微镜检查是对具有两种不同故障类型的多个故障器件进行的。

检查这些器件后发现,具有软故障(“A”型)特征的子集在 MOSFET 的 JFET 间隙中有栅极氧化物破裂(见图 4(a))。另一方面,那些具有硬故障(“B”型)特征的器件在 MOSFET 的 n+ /p 阱区域有栅极氧化物破裂(见图 4 (b))。这不仅仅是巧合:它在许多器件中都是可重复的,并且可以通过考虑 poly-SiO2-SiC 界面的能带图来解释。

热心的读者可以在今年早些时候发表的一篇论文中找到我们的详细解释(详情请参阅“扩展阅读”)。在这里,我们提供了一个更简单的替代方案。我们认为,在随时间变化的介电击穿应力期间,如果 SiO2 中存在栅极氧化物破裂,则这可能会将多晶硅-SiO2-SiC 界面转化为基本的肖特基结。对于位于 p 阱上方的聚 SiO2-SiC,多数载流子空穴将在较大的负栅极偏压下积聚在那里。同时,对于 n+ 源上的聚SiO2-SiC来说,即使在负栅极偏压下,多数载流子的丰富程度仍将保持。但是,当破裂发生在低掺杂 n 型 SiC JFET 间隙区域时,情况就不同了。在这种情况下,电子将在类似的偏压条件下耗尽。这与我们的电气测量结果一致--并解释了为什么当栅氧化物击穿发生在 n+ 或 p 阱区域时,在大负栅偏压下的电流比在耗尽的n型SiC JFET间隙中破裂时的电流高得多。

对于正偏压下的破裂区域,电流在正偏压下始终很高,因为电子积累可能发生在 n+ 源和 n 型 SiC JFET 间隙区域。在 p 阱上方发生故障的情况下,即使在正偏压下 p 阱和 poly(/SiO2) 界面处的多数载流子空穴会被耗尽,但由于 p阱中的反转电子,仍然存在高电流。因此,无论栅极氧化物破裂是发生在n型JFET、p-阱还是n+区域,所产生的栅极电流水平在正栅极偏压下都将保持较高水平。

我们的研究表明,在正常操作和加速的负栅极偏压条件下,从我们的器件中提取的栅极氧化物寿命与从正栅极应力中提取的栅极氧化物寿命非常接近。这项工作应该有助于减轻对空穴传输而非传统电子传输下的栅极氧化物寿命和故障模式的任何担忧。虽然我们的研究考虑的是平面MOSFET 设计,但类似的观察结果有可能适用于其他元胞设计,例如采用沟槽的元胞设计。然而,在做出任何声明之前,需要进行实验验证。我们研究的另一个重要发现是,在负栅极时间依赖的介电击穿应力下存在的不同电气故障特征与 MOSFET 元胞中的故障位置相关。这一观察有望帮助任何新工艺开发的早期阶段,因为它将允许从栅极泄漏数据中识别故障位置,而无需进行物理故障分析。我们希望这种见解,以及我们研究提供的其他见解可以帮助 SiC 世界更加强大!

扩展阅读

A.J. Lelis et al. “Basic Mechanisms of Threshold-Voltage Instability and Implications for Reliability Testing of SiC MOSFETs,” IEEE Trans. Electron Dev. 62 316 (2015)

D.J. Lichtenwalner et al. “Reliability Studies of SiC Vertical Power MOSFETs,” IEEE International Reliability Physics Symposium (IRPS) 2B.2-1–2B.2-6 (2018)

J. McPherson et al. “Comparison of E and 1/E TDDB models for SiO2 under long-term/low-field test conditions,” IEDM 171 (1998)

S. Ganguly et al. 1998 “Negative Gate Bias TDDB evaluation of n-Channel SiC Vertical Power MOSFETs,” IEEE International Reliability Physics Symposium (IRPS) 8B.1-1-8B.1-6 (2022)

图 1. 单极性一维特定半导体漂移导通电阻(RON,SP,单位为mΩ-cm2)与击穿电压的关系。橙色虚线和黑色虚线分别表示硅和SiC在室温 (RT) 下的理论极限。RT 数据点代表Wolfspeed SiC MOSFET的各代产品和额定电压,绿色虚线是该数据的视觉指南。改编自J. W. Palmour et al., Proceedings of the 26th International Symposium on Power Semiconductor Devices & IC's, June 15-19, 2014.

图 1. 单极性一维特定半导体漂移导通电阻(RON,SP,单位为mΩ-cm2)与击穿电压的关系。橙色虚线和黑色虚线分别表示硅和SiC在室温 (RT) 下的理论极限。RT 数据点代表Wolfspeed SiC MOSFET的各代产品和额定电压,绿色虚线是该数据的视觉指南。改编自J. W. Palmour et al., Proceedings of the 26th International Symposium on Power Semiconductor Devices & IC's, June 15-19, 2014. 图 2. Wolfspeed Gen3 MOSFET 时间依赖电介质击穿 (TDDB) 中值失效时间 (MTTF) 与 175℃ 时的栅极应力电压的关系。红色数据点代表在测试的栅极应力电压下提取的 MTTF 值,而实线是文本中描述的拟合和推断。星号代表基准点,以说明在推荐的工作栅极电压应力条件(正和负)下的预测 MTTF 寿命。改编自:S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022.

图 2. Wolfspeed Gen3 MOSFET 时间依赖电介质击穿 (TDDB) 中值失效时间 (MTTF) 与 175℃ 时的栅极应力电压的关系。红色数据点代表在测试的栅极应力电压下提取的 MTTF 值,而实线是文本中描述的拟合和推断。星号代表基准点,以说明在推荐的工作栅极电压应力条件(正和负)下的预测 MTTF 寿命。改编自:S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022. 图 3. 室温下时间依赖性介质击穿后负栅极应力失效。具有两个不同故障特征(“A”:软故障,“B”:硬故障)的器件的典型栅极泄漏与栅极电压电流扫描数据。在正扫描 (VGS > 0) 期间,“A”和“B”的漏电水平相似,而在负扫描期间 (VGS < 0),“B”的泄漏水平比“A”高几个数量级。改编自:S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022.

图 3. 室温下时间依赖性介质击穿后负栅极应力失效。具有两个不同故障特征(“A”:软故障,“B”:硬故障)的器件的典型栅极泄漏与栅极电压电流扫描数据。在正扫描 (VGS > 0) 期间,“A”和“B”的漏电水平相似,而在负扫描期间 (VGS < 0),“B”的泄漏水平比“A”高几个数量级。改编自:S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022. 图 4. 横截面示意图以及聚焦离子束、横截面扫描电子显微镜图像,显示了负栅极偏压时间依赖性介质击穿 (TDDB) 后的栅极氧化物破裂:(a) 在 JFET 间隙中的“A”型 ' 软故障电气特征,(b)在 n+ /p 阱的'B' 型硬故障电气特征 。改编自 S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022.

图 4. 横截面示意图以及聚焦离子束、横截面扫描电子显微镜图像,显示了负栅极偏压时间依赖性介质击穿 (TDDB) 后的栅极氧化物破裂:(a) 在 JFET 间隙中的“A”型 ' 软故障电气特征,(b)在 n+ /p 阱的'B' 型硬故障电气特征 。改编自 S. Ganguly et al., IEEE International Reliability Physics Symposium (IRPS), pp. 8B.1-1-8B.1-6, 2022.

| 上一篇:拥护真正的重量级材料:... | 下一篇:全球首次采用垂直布里奇... |