技术文章详细内容

将microLED与先进CMOS集成

2023/3/24 7:09:47 材料来源:

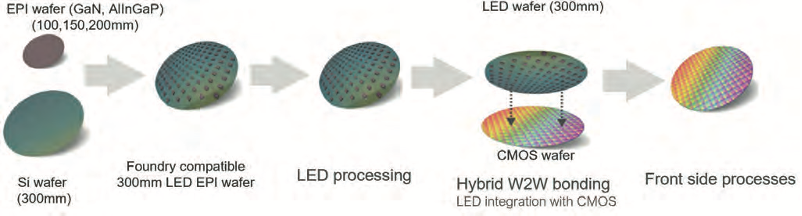

将300 mm硅基GaN LED晶圆键合到相同尺寸的CMOS背板上,是生产microLED间距仅为几微米的显示器的最佳方法。

作者:SOREN STEUDEL,MICLEDI MICRODISPLAYS

在过去五年左右的时间里,microLED制造一直是显示器行业的热门话题。在 Display Week 等领先的显示器盛会中,它一直处于重要议程,重点是各种显示器的平板制造,尺寸范围从智能手表到手机和电视。对于这项技术,与microLED的巨量转移以及缺陷芯片的修复相关的挑战,阻碍了规模化生产的扩大。

当考虑将microLED用于微显示应用时,会面临一系列新问题,如增强现实(AR)眼镜。

为该类型应用制作microLED显示模块的一种方法是将microLED和CMOS-ASIC背板集成起来,后者控制和驱动microLED。该方法消除了与巨量转移相关的问题,但却遇到了一系列其他障碍。考虑一下这项技术的主要应用,即AR眼镜,需要亮度超过1 Mnits,像素间距低于3 µm、分辨率高达2K以上、超低功耗和可接受的成本,所有这些都要在一个轻型模块中实现。

到目前为止,现有的微型显示器制造方法还不能满足所有这些规范,仍在努力中。中国上海的芯片制造商JBD已经推出了几款令人印象深刻的原型设计,并且正在交付适量的产品。然而,难以实现大批量生产。与此同时,比利时鲁汶的MICLEDI Microdisplays公司,在解决限制microLED显示器亮度和分辨率的问题上取得了很大进展。为此,我们正在开发一种实现大批量、低成本制造所需的方法。请继续阅读,以了解我们所面临的挑战和我们引人注目的解决方案的细节。

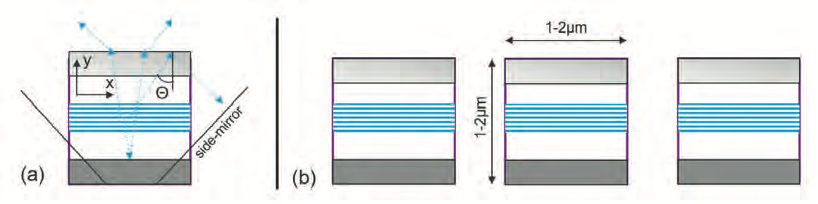

图1.具有(a)小像素与(b)窄间距阵列的平面microLED中的光输出耦合。

亮度和效率

AR眼镜的一个缺点是它们非常大的光学损耗。这种损耗的程度由实施情况决定,但通常只有不到1%的显示器发出的光子到达眼睛。由于这些惊人的损耗,显示器必须产生高达1000万尼特的白光,以支持户外使用高透明度眼镜。

microLED 显示器的竞争技术是类似 microOLED 的显示器,即使OLED的效率比microLED更好,在最佳情况下也可以实现2万尼特的绿色。法国市场分析机构Yole Intelligence对2019年最新技术的总结显示了 OLED (RGB 22%,22%,7%)与 5 µm的 microLED(RGB - 7%,15%,25%)的效率数据。请注意,这些数字远远低于氮化镓LED的内部量子效率值,其典型值为蓝色 85%、绿色 60% 和红色不到 30%。

缩放尺寸下的效率损失主要是由于光外耦合,在较小程度上是由于台面侧壁缺陷导致的电损失,导致大量的非辐射复合和增加的漏电流。平面LED中的光外耦合受限于从高折射率

材料到空气的内反射角度。这意味着,对于GaN LED来说,在忽略干扰效应的情况下,只有不到 10% 的光可以通过完美的背面镜提取。对于尺寸大于100 µm 的大型LED来说,表面纹理采用非常好的背面镜。这使每个光子在不同的角度下都有多次输出的机会,从而使理论上的光提取效率达到75%。表面纹理不是尺寸低于 5 µm 的 microLED 的解决方案,因为光子没有空间进行多次反射。

值得注意的是,Yole提供的效率非常乐观,只适用于间隔很远的单个LED。图1说明了这一点,该图考虑了不同的间距场景。在microLED中,通过透明的正面触点的直接发射非常低,通常低于10%--但可以通过添加侧壁镜来提高提取率,该侧壁镜可以提取超过内部反射角度的光。然而,当将microLED封装在一起以确保更高的间距时,任何类型的侧壁镜都不太有效。由于这一障碍,microLED在极小的显示器中的外部量子效率预计将限制在不超过8%,除非转向定向发射器架构。

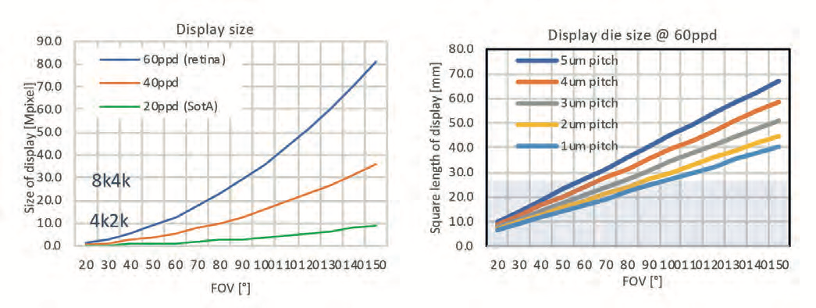

图2((左)不同角度分辨率下视场(FOV)与像素数的函数关系图(Mpixel指的是1个具有红-绿-蓝子像素的像素,显示比例为1:1);(右)不同子像素间距的芯片尺寸(假设高级节点CMOS(<45nm),具有帧缓冲区和16:9的显示比例)。

图3. 不同子像素间距的芯片成品率与视场(FOV)的关系。(左)假设 RGB 逐像素;(右)假设 RGB 逐晶粒。

因此,鉴于microLED效率低,这些器件仍然被视为OLED的可行替代品,因为它们具有非常出色的电流处理能力。由于能够维持比OLED高一千多倍的电流密度,这些基于GaN的器件可以提供目标亮度。

显示屏尺寸和分辨率

任何基于microLED的显示器都有两个问题:它所需要的尺寸是多少?什么分辨率是合适的?要回答这些问题,必须考虑人眼的能力。在绿色和蓝色光谱域中,人眼的角度分辨率为每度60像素。我们在考虑AR眼镜的目标视野时注意到了这个数字。正如人们所期望的那样,当增加视野或角度分辨率时,显示器中的像素数量必须增加(参见图2,左)。在目前的一些商业头盔式AR中,系统支持全高清显示,但视场范围有限,只有50°。从 5 µm 到 1 µm的microLED的一个好处是,它们可以在相同的显示器尺寸下提供更大的视野(参见图2,右)。

尽管这种小型化水平很有吸引力,但要想实现常规的成功却远非易事。即使是制造间距为5 µm的全高清显示屏,也会接近曝光工具的视网膜尺寸极限。接近该极限的操作会影响可制造性和良率。

我们计算了不同间距对良率的影响。根据我们的制造良率模型(参见图3,左)--假设红色、绿色和蓝色microLED并排集成--即使目标分辨率降低到每度仅40像素,也需要小于3 µm的间距才能超过50%的良率。

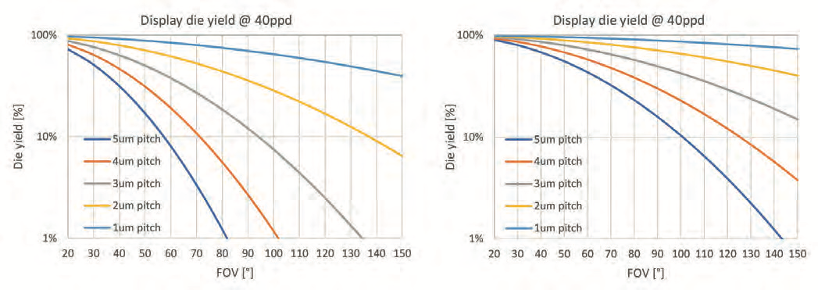

图4. microLED-CMOS集成方案概述。

通过独立制造三种不同颜色的发射器,然后将它们与光学组合器集成在一起,可以显著放宽这些条件(参见图3,右)。这就更接近于现有彩色显示技术的良率模型,称为硅上序贯液晶显示器。

可制造性

在过去的十年中,几个研究小组已经将microLED的尺寸缩小到1 µm以下。然而,对于这些研究人员来说,考虑将LED像素与CMOS驱动电路(通常称为“背板”IC)集成通常只是事后考虑。(页面绿色加粗强调部分)可以采取多种方法来实现这种集成(图4中总结了各种选项)。一种是晶粒到晶圆的转移,通过一次转移和放置一个像素来创建红色、绿色和蓝色发射器阵列,或者通过将整个阵列粘合为单个小芯片来实现。这两种晶粒到晶圆的转移都采用了铟凸点,这种技术已经在红外成像仪的大规模生产中使用了20多年。晶粒到晶圆转移的另一个优势是,它允许在标准的CMOS晶圆厂中制造CMOS背板,而在

晶圆厂中制造前板二极管阵列--每个晶圆厂都根据特定的晶片尺寸定制,并使用专用工具集。采用这种方法,在出现明显的良率损失之前,生产可以很好地扩展到10 mm的间距。还有其他类型的微凸点以及混合键合的晶粒到晶圆方法。

对于军事和太空应用,已使用晶粒到晶圆键合生产间距低至 4 µm的紫外和红外成像仪。

然而,良率非常低--这对显示器行业来说是不可接受的。因此,对于 microLED 显示器,需要采用完整的晶圆到晶圆方法来达到 10 µm 间距以下并将 LED 与背板结合起来。如果要与顺序3D方法一起使用晶圆对晶圆的键合,那么LED阵列晶圆和CMOS晶圆必须具有相同的尺寸。这就带来了一个问题:与OLED显示器相比,microLED需要更复杂的驱动和补偿方案,例如包含帧缓冲器,因此必须使用远低于 45 nm 的先进节点在 300 mm 晶圆上制作附带的硅电路。由于没有批量生产 300 mm的

外延片, 目前的努力方向是将较大的CMOS晶圆尺寸调整为直径100 mm或150 mm,从而导致昂贵的晶圆面积损失。混合键合的进展也因需要极端的表面平面性,以及非常低的晶圆弯曲度和通常低应力而受到阻碍。几乎所有通过异质外延沉积的

堆栈都难以满足所有这些要求。

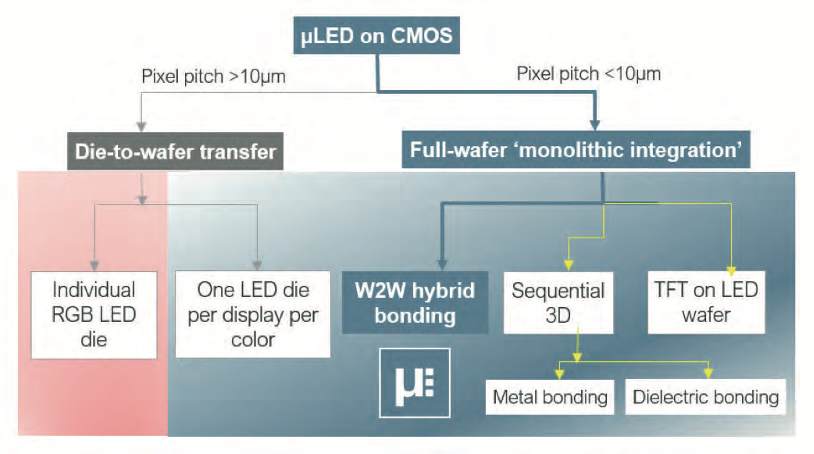

图5.从300 mm

重构到二极管阵列与先进节点CMOS的混合键合的制造流程。

令人鼓舞的是,堆叠硅晶圆的生产工艺已经投入使用,将顺序 3D 结构与衬底通孔和晶圆到晶圆的混合键合相结合。后者通常用于生产间距小至3 µm的背面照明成像器,并用于研发部门,以间距小于1 µm的300 mm晶圆与小于200 nm的覆盖层结合起来。

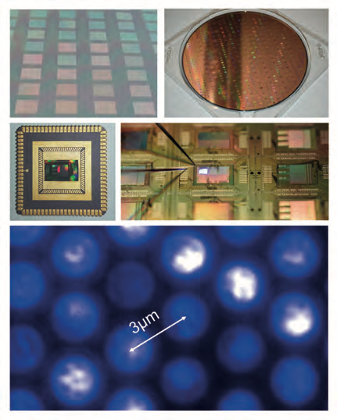

图6. 300 mm LED晶圆的图像

(a)在GaN重构后;

(b)经过完整的晶圆到晶圆的集成方案;

(c) 封装后的裸片;

(d) 具有 9150 ppi 的 480 x 320 无源阵列。

显示器集成

我们公司是imec的子公司,于2019年推出,其使命是解决上述的可制造性和良率问题。在开发我们的显示器技术时,我们所做的决定遵循以下三个前提:我们的集成流程是在300 mm 的生产设备上开发的,因此可以转移到CMOS代工厂;我们选择的材料尽可能与先进的CMOS 晶圆厂的污染和废物管理协议兼容--因此这意味着没有银、金或砷化镓;并且在制造其他产品时,尽可能采用既定的工艺步骤和模块,这些步骤和模块能够提供高良率。

考虑到这些要求,我们开发了一种LED集成工艺,该工艺与用于制造 3D 背面照明成像仪的工艺非常相似。然而,在我们的案例中,我们将硅光电二极管晶圆替换为填充有 GaN 二极管的晶圆(参见图 5)。我们通过从多家供应商采购同类最佳的商业外延片,克服了初始GaN材料的局限性,例如尺寸小、应力和弯曲度大以及颗粒密度高。在重新分布到空白硅晶片上之前,Epi裸片被切割成最终显示器的尺寸,例如4 mm x 6 mm以实现全高清晰度。在去除外延生长衬底和缓冲层并对其进行平坦化处理后,我们使用预先选择的已知良好外延芯片制作了直径为300 mm的无应力结构,从而仅剩下1.5 µm厚的GaN堆叠,其特征是有一个有源区夹在掺杂层之间(见图6(a))。从晶圆处理的角度来看,这种重组晶圆的行为类似于硅晶圆。

.png)

图7. 具有7.5 mm网格的红色硅基GaN线性阵列的电致发光图像。

在300 mm 的晶圆上加工出3 µm间距的LED。随后的晶圆到晶圆的混合键合将该晶圆与300 mm CMOS背板ASIC晶圆结合在一起,其对准精度超过250 nm。对于我们最初的工艺开发、器件表征和取样,我们使用了只有几层金属层的硅晶片,将操作限制在对矩阵阵列的无源控制上(参见图 6 (d) 对 480 x 320 像素的无源阵列进行晶圆级测试;图 6 (c) 为封装裸片的图像;和图 6 (e) 为具有 3 µm 间距和 2 µm 台面的阵列的显微图像)。我们的下一步是用实际的ASIC来替换这些无源阵列。

使用这种集成方案,我们实现了高达65%的创纪录孔径,在3 µm的六角形间距配置中,孔径为2.5 µm。这种大孔径是一个巨大的特性,对实现高亮度至关重要。首批下线的蓝色发光晶片在5V下的亮度为60万尼特。对于这些发射器,外部量子效率超过了2%。

我们目前的方法是用光学组合器将红色、绿色、蓝色芯片的输出汇集在一起。这种方法的一个含义是,我们必须对所有三种形式的芯片使用相同的工艺流程。不出所料,最大的挑战是红色LED。我们正在努力提高效率和色点。图7中可以看到由200 mm硅基GaN外延片形成的红色光源的第一个短路样品。

改进晶圆级光学器件为提高性能提供了另一种途径。通过增强对波导集成有用的顶角内的光输出耦合并抑制该角度外的光发射,应该可以将亮度提高 2 到 4 倍。在相对较短的时间内,我们已经证明,对于5 µm 及以下的间距,转向将 300 mm microLED 晶圆键合到 CMOS 背板晶圆的单片方法有很多优点。通过与 imec 的合作伙伴合作,我们已经解决了与该工艺相关的挑战,现在我们开始将技术转让给我们的代工厂合作伙伴。

作者在此感谢与 imec 300 mm 试验线和 imec 3D 集成部门的合作。

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

GaN功率应用线上会议

4月13日下午14点,ACT雅时国际商讯& 杂志联合推出“GaN功率应用,厚积薄发”线上研讨会,以期推动GaN功率应用产业的加速成长。报名从速:https://w.lwc.cn/s/nuIBBb

| 上一篇:氧化镓晶体生长方法的选... | 下一篇:钙钛矿CIGS串联产生24.... |