技术文章详细内容

超结 器件

2022/8/1 7:52:04 材料来源:

凭借巧妙的电荷平衡结构,

功率器件正超越其极限。作者:ONSEMI JAN CHOCHOL和ROMAN MALOUSEK

凭借巧妙的电荷平衡结构,

功率器件正超越其极限。作者:ONSEMI JAN CHOCHOL和ROMAN MALOUSEK

整个电力电子行业都在进行

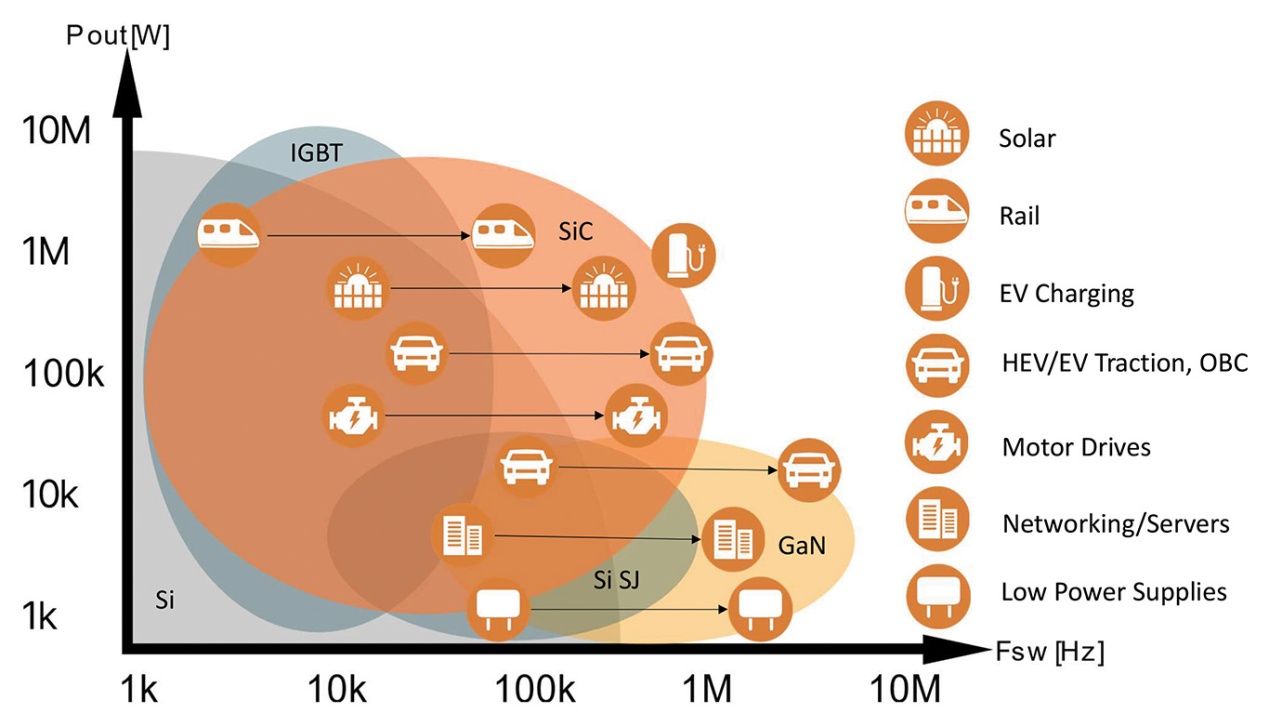

活动。毫无疑问,SiC器件的介电击穿场强是硅的十倍,电子饱和速度是现任器件的两倍,带隙的三倍,热导率是硅的三倍。所有高功率应用都受益于这些特性,如图1所示,因此供应商、晶圆厂和OEM正在接受

的快速采用也就不足为奇了。所有人都在努力超越竞争对手。

图1:不同电力电子技术的应用领域

由于所有这些疯狂的活动,该行业出现了一些混乱,为各种发展创造了机会。这促使我们的onsemi团队探索各种概念。在

行业日趋成熟的背景下,我们能够重新探讨一些仅在几年前还不可行、成本过高或当时可用的工具集显然不可能实现的主题。

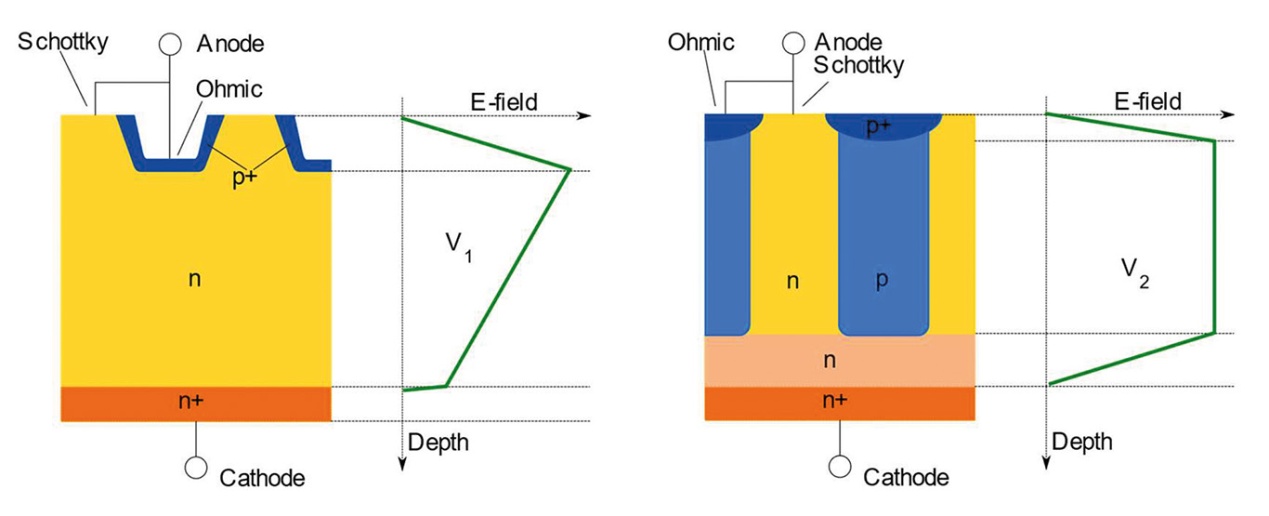

其中一个概念是超结。无论设计如何,任何由

制成的器件都将受益于其独特的性能。它们包括一个大的击穿场,它可以剃掉几十微米的外延厚度,与硅相比,在给定的额定电压下,大大降低了导通电阻。但有了我们所探索的超结结构,我们可以更进一步。通常,这种结构由交替区域组成,这些区域高度掺杂,间距紧密,掺杂相等和相反,这是一种确保电荷平衡的架构。有了这样的结构,高掺杂会产生更好的传导,从而降低电阻。但这并不是我们在反向偏压下操作的唯一好处,超结完全耗尽,电场以近似矩形均匀分布。由于这一点,与经典的单极漂移区(其中电场必须是梯形的)(见图2)相比,我们在相同的漂移厚度下实现了更高的击穿场。

图2:具有单极漂移区(左)和超结JBS二极管(右)的JBS二极管示意图

真正的问题是,我们如何构建这样一个结构?我们需要有明确的支柱,其可控浓度达到表面以下几微米。由于每微米的超结深度可以阻挡约200 V(我们将继续展示),因此1200 V的器件需要超过6μm的受控超结柱。

形成柱的一种选择是离子扩散。然而,那些在

社区工作的人并不太关心这项技术,因为根本没有办法在

中扩散离子。这导致一些团体和公司尝试了其他方法,例如CVD填充沟道。

重提离子注入

但在我们的初步研究中,由于方法的简单性和工具的可用性,我们决定重新审视离子注入。我们研究了两种不同的技术。其中之一涉及使用非常高能量的离子注入。粗略地说,这是一种粗暴手段;由于其高动能,我们将离子深注入

。更高的能量意味着更深的渗透。然后,使用多个注入离子,我们可以将浓度分布链在一起,以创建一个看似均匀的分布。这种方法需要注意的是,我们必须保护另一根柱不被注入。因此,一个注入物可以是覆盖物,而另一个必须被遮盖,剂量是另一个的两倍。成功并不容易,因为只有如此厚的光刻胶才能阻止注入。

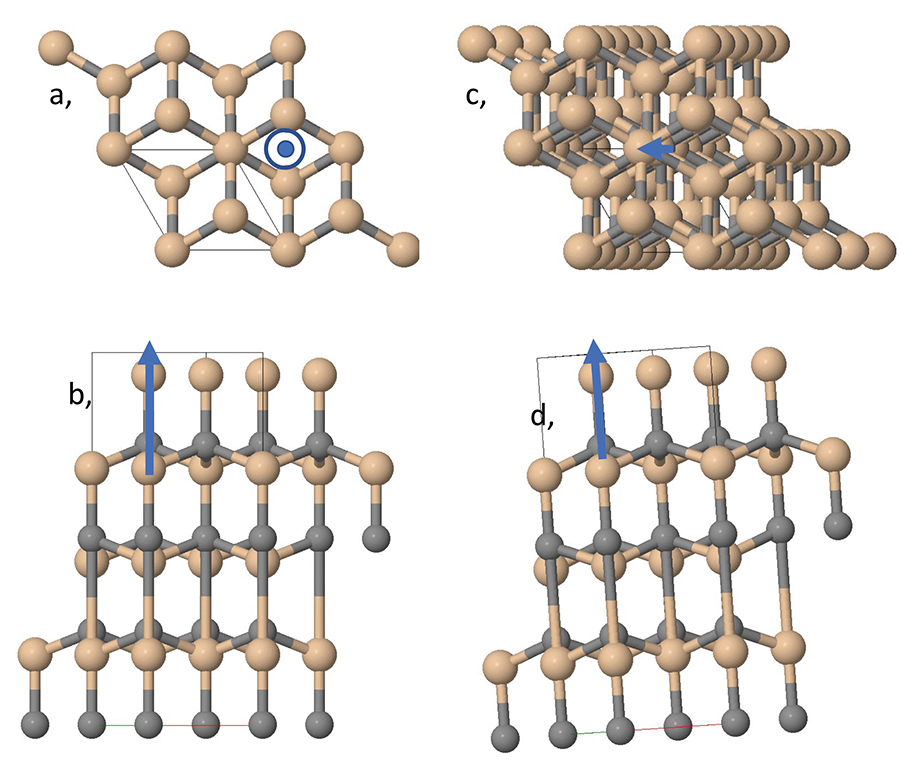

图3:4H-SiC晶格的JMOL模拟。蓝色箭头表示晶体的c轴方向。(a)通过通道方向查看;(b)侧视图;(c)倾斜晶格;(d)倾斜晶格侧视图。

由于这一局限性,我们还探索了沟道注入。用于电力应用的4H多晶

的一个关键特征是,它允许离子沿着优先角度注入,离子“穿透”晶格,离子-晶格碰撞的数量急剧下降。这一原理如图3所示,导致浓度分布比随注入方向下通常可能的浓度分布要深得多、平坦得多。例如,一个900 keV的非沟道铝注入的深度可达0.7μm,而利用该能量的沟道将深度扩展到3μm。

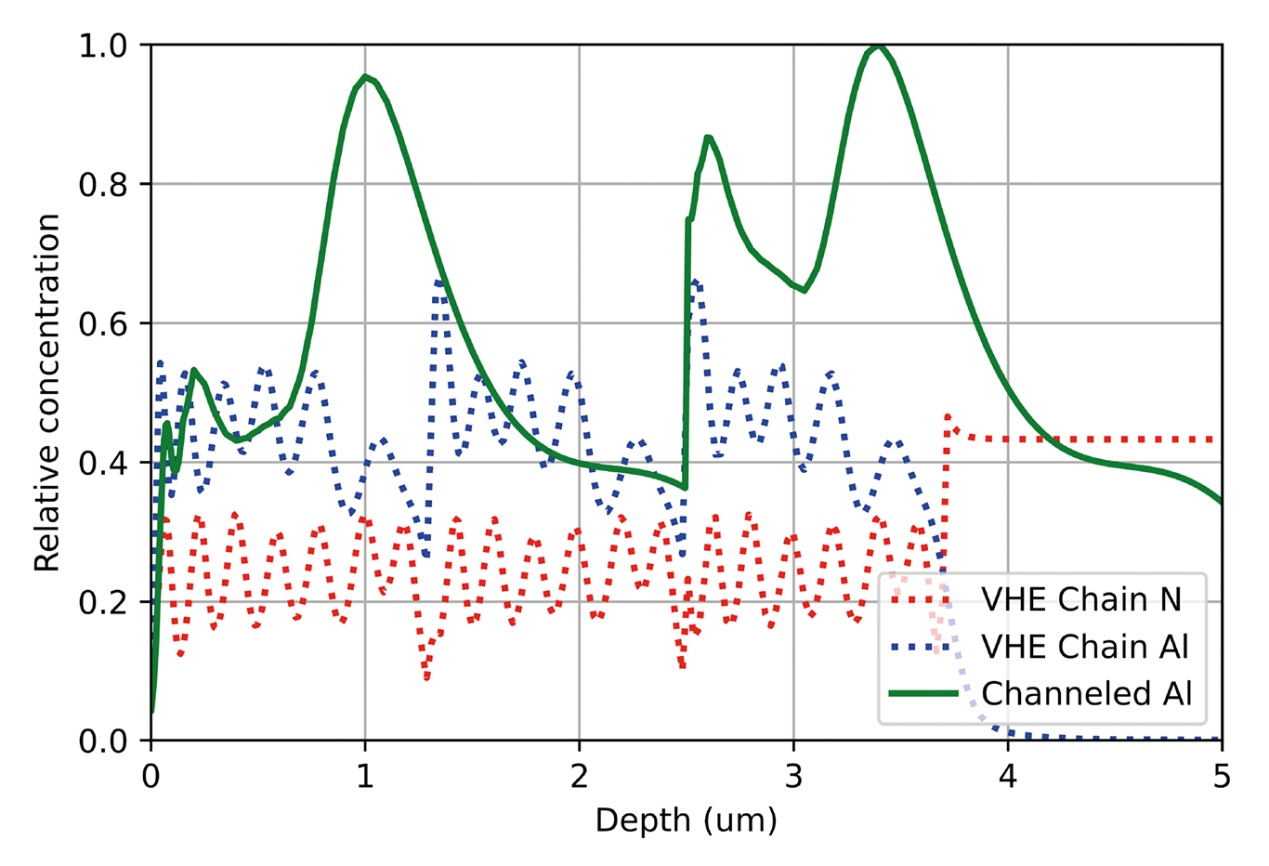

通过这种方法,我们将包层高能氮注入技术相结合,制备出了柱状物,而不需要掩模沟道铝注入的掩模。通过二次离子质谱获得的剖面图可以看出该方案的成功(见图4)。

图4:超结实验中注入剖面的SIMS数据

沟道方向沿晶体的0001方向——也是晶体生长的方向。由于大多数商用

晶体是在4 °角度,这是我们使用的通道角度。为了产生定义良好的柱,注入工具在晶圆和批次之间保持最佳角度至关重要。我们非常感谢Nissin Ion Equipment的支持,在我们的试点研究中,他们帮助了我们。

无论我们采用沟道还是高能注入,都需要外延再生长步骤才能达到所需的厚度。在重新启动每个新柱层的外延工艺时,我们仔细调整了条件,以尽量减少注入材料(回蚀)的任何潜在损失,并确保整个外延结构的浓度恒定。我们面临的另一个挑战是在每次外延再生长后调整掩模的对齐标记,并更新标记以确保后续层的精确位置。对于超高能注入形成的结构,我们进行了三个外延层生长步骤,每个步骤涉及1.2μm厚的沉积层;对于沟道运行,我们只使用了两个生长点,每个2.45μm厚。我们用这两种结构制作了结势垒肖特基二极管。这涉及到使用平行条纹作为柱的掩模。由于这些条纹平行于晶圆平面,我们在进行沟道注入时避免了掩模阴影。

评估不同片芯

为了全面评估我们的器件性能,我们制作了小(0.0012 cm-2)和大(0.018 cm-2)管芯。小管芯使我们能够研究多种设计,而大管芯具有更类似于生产线器件的特性。对于超结器件,必须确保适当的电荷平衡。这意味着两个柱的掺杂浓度相同。在任何工艺中,都有一些将导致浓度扩散的因素在起作用。但可以通过改变条纹宽度来解决这一问题,因为这提供了一种补偿和调整设计的机制——较宽、较低掺杂的柱将与较窄、较高掺杂的柱表现相同。我们在p型柱的顶部注入了浅、高剂量的铝,以确保良好的欧姆接触。

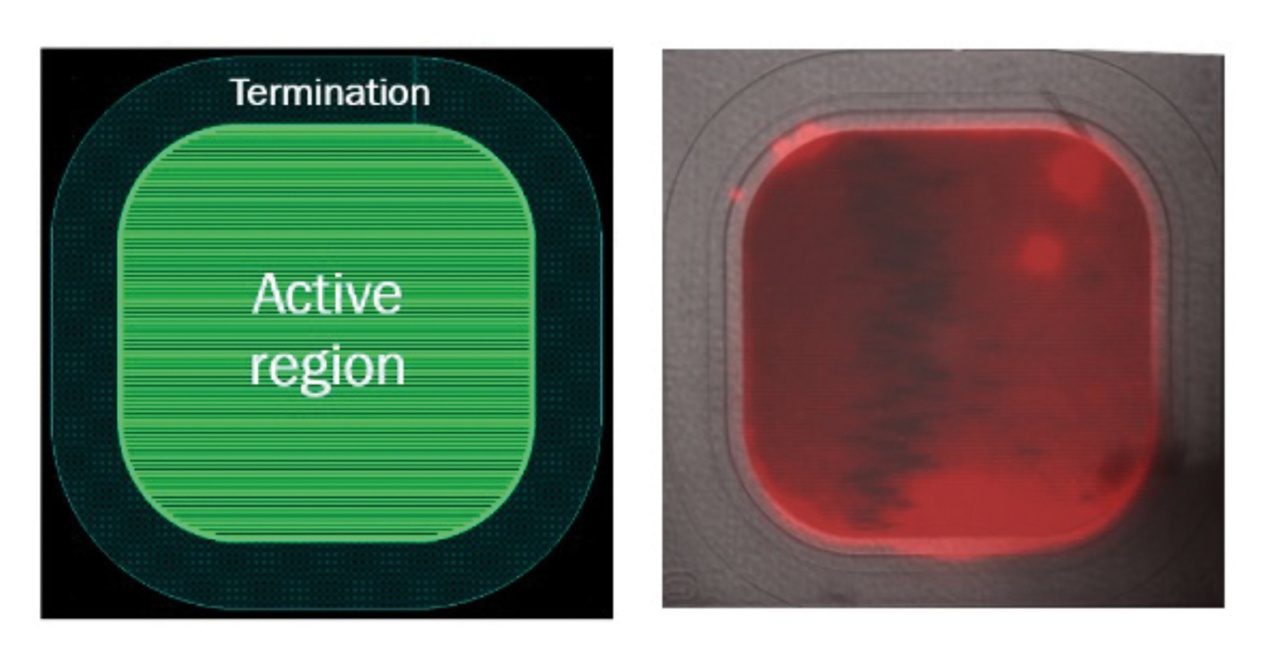

与我们器件的连接采用标准

工艺,在正面增加了钛/锡肖特基/欧姆接触。我们转而对阴极接触进行背面研磨和金属沉积。我们的器件具有端接功能,用于扩展电场并在有源区均匀分布雪崩电流。我们验证了这是通过电致发光实现的,电致发光显示了有源结构中的均匀击穿(见图5)。

图5:左:器件设计示意图。右:雪崩击穿中器件的电致发光

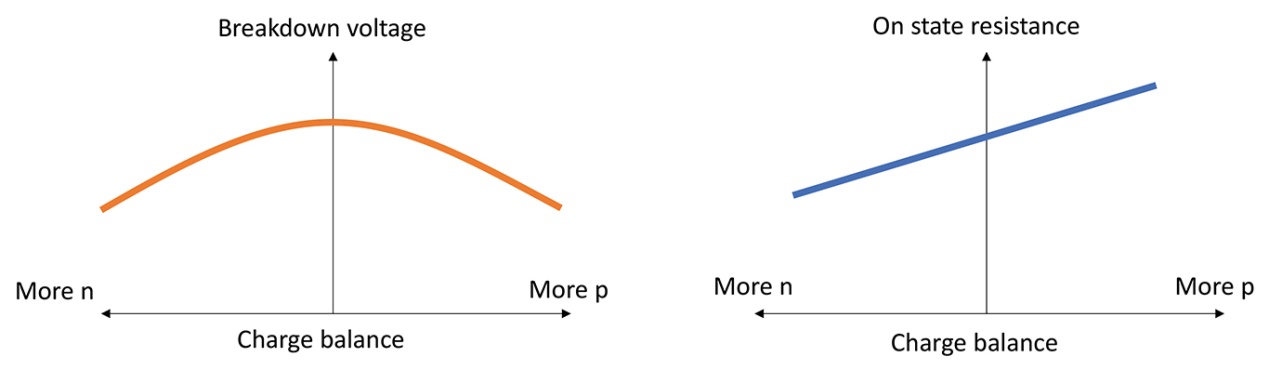

在深入研究我们的超结研究结果之前,值得考虑我们对预期行为的假设。关键特性是二极管的击穿电压及其导通电阻。理想的情况是在柱浓度中有完美的1:1比率,因为这确保了在给定的超结厚度下可实现的最大击穿电压。同时,导通电阻与发生传导的n型浓度成线性比例(行为如图6所示)。

图6:超结器件的预测行为

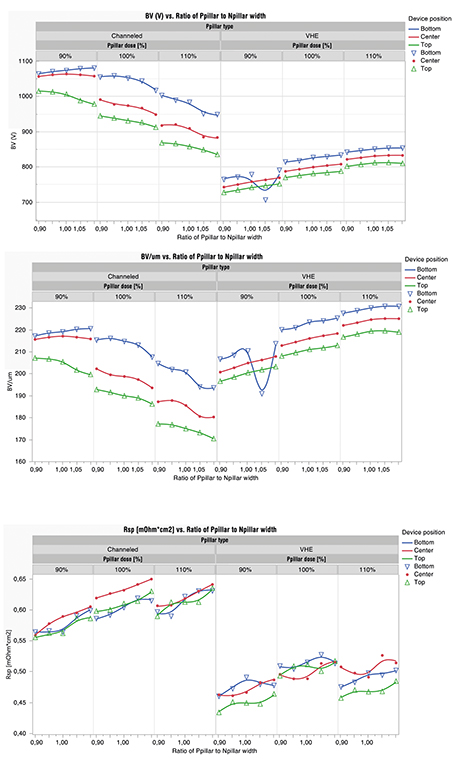

我们研究的实际结果(如图7所示)证实了我们的假设。我们为每个注入方案使用了三个晶圆,每个晶圆的剂量略有不同(±10%),并在器件设计中改变了柱比。我们的击穿结果遵循抛物线形状,绝对位置由超结的厚度决定。请注意,在晶圆上的分布,靠近平面的较厚外延结构提供了较高的击穿电压(优化均匀的晶圆分布不是研究的一部分)。正如预期的那样,导通电阻随着p型柱的宽度和外延厚度的增加而增加。我们讨论了晶圆之间导通电阻的变化与衬底电阻的变化。

图7:来自超结器件表征的电气数据

为了比较超高能注入和沟道实现的结果,我们按厚度对击穿值进行了归一化。在忽略外延厚度扩展后,两种方法都产生了约210V/μm的击穿。这是一个至关重要的发现,意味着两种方法在电气性能和工艺稳定性方面是相同的。不同之处在于所需的工具集和所需的外延步骤数量。

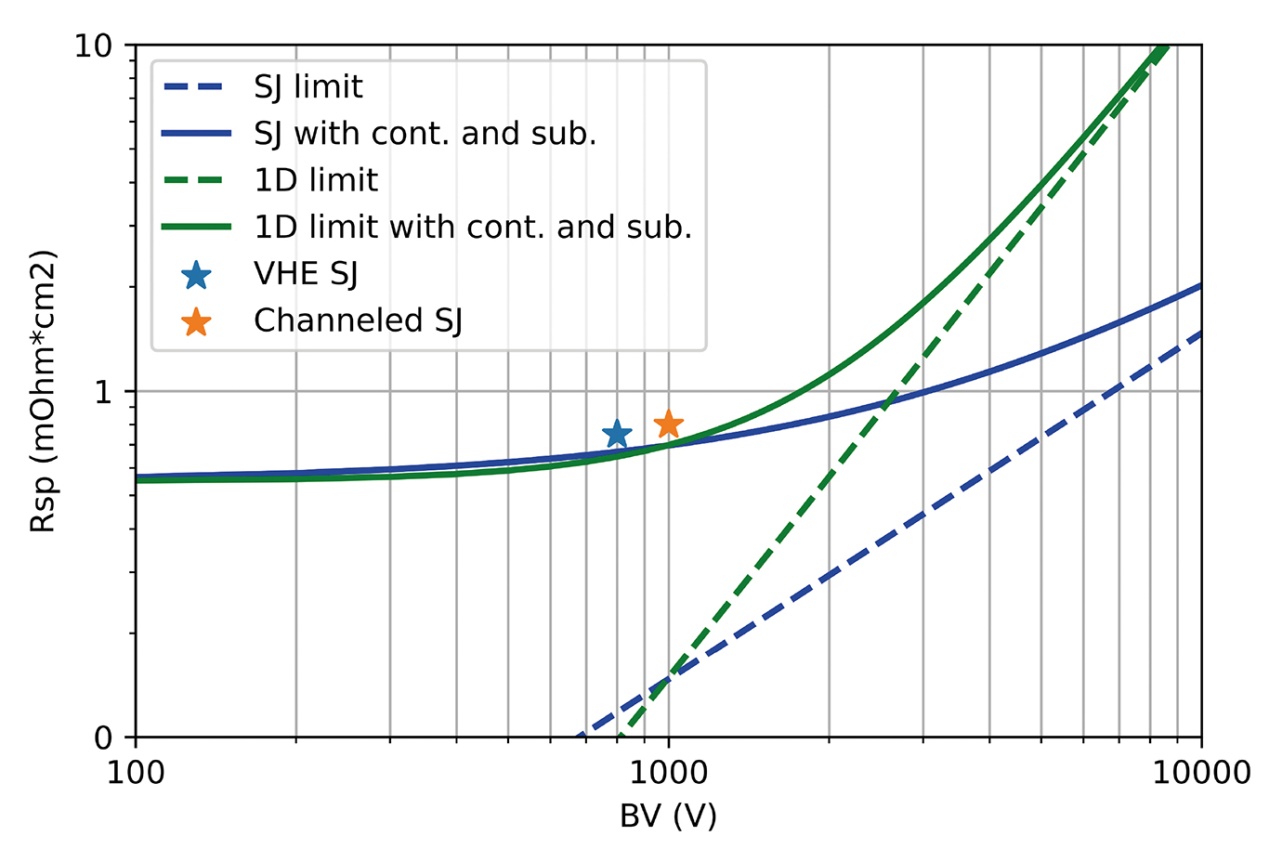

有了手头的数据,我们可以将我们的器件与具有经典架构的器件进行比较,包括具有单极漂移区的变体。我们的评估包括这种器件的一维理论极限图,可以比较导通电阻和击穿电压(见图8)。我们看到,通过我们的测试器件,在更大的芯片上进行的测量表明,我们正处于1000 V/0.7 mΩ cm-2的临界点。通常,在3 kV-5 kV区域,使用超结器件的最佳点高于此范围。

图8:单极和超结器件击穿电压和导通电阻的折衷曲线与实验数据

然而,这只是等式的一个方面。

器件也因其高温性能而备受追捧,几乎在其所有应用中都发挥着重要作用。在这里,超结将“超级”放入器件。漂移区是阻挡场扩散的区域,是器件的最低掺杂部分。正是在这里,对器件电阻有很大的贡献,但超结的引入使该区域更薄和高度掺杂,正如我们所看到的,在1000 V阻断电压后,这种变化得到了回报。

由于该区域的高掺杂,器件受温度引起的电阻增加的影响较小。结果是,即使在更高的温度下,该器件仍保持其低电阻。与此同时,故障基本上没有受到影响。事实上,由于声子散射增加,需要更多的能量来推动电子雪崩。因此,正如我们所展示的,用超结取代漂移区会带来回报,将普通器件转变为在高要求应用中表现出色的器件。

如果不扩大整个

生态系统,

器件的采用及其相关发展,包括本研究中报告的进展是不可能的。无论是制作衬底,都涉及晶圆、研磨、抛光;或外延生长或其他前端或后端过程;每一步都是一项要求很高的操作,需要利用来之不易的专业知识和专业工具。

SiC最初是onsemi通过收购飞兆半导体(Fairchild)获得的,从那时起,器件技术一直是由以下各方密切合作开发的:瑞典Kista的设计中心;韩国布川的设备和工艺集成团队;以及缅因州南波特兰的工程团队负责开发SiC外延技术。

我们目前的职责包括支持韩国布川和捷克Rožnov pod Radhoštěm关键晶圆厂的

开发和生产。Rožnov是一个坐落在贝斯基德山脉的小镇,材料开发受到了广泛关注,并获得了该地区最具创新性公司奖。

随着最近收购

衬底制造商GT Advanced Technologies,我们公司提高了垂直整合水平,巩固了

器件组合。这些举措巩固了我们在电力电子行业中的重要地位,并磨砺了

技术的前沿。

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

| 上一篇:钙钛矿PV有30年寿命? | 下一篇:Wolfspeed 模块产品组合... |