提升 GaN 阻断电压

2021/9/14 18:53:14 材料来源:

p 型 NiO 的溅射层使硅基 GaN 肖特基势垒二极管的阻断电压几乎翻了一番

来自瑞士 EPFL 的工程师声称已经打破了硅基 GaN 肖特基势垒二极管的击穿电压记录。该团队的器件采用 p 型 NiO 层作为结终端扩展,能够阻止高达 443 V 的电压。

结终端扩展是常见的结构,广泛应用于硅和 SiC 器件中,以防止电场的局部峰值并最终确保更高的阻断电压。

然而,在这些器件中,结终端扩展是通过注入或扩散形成的,以创建选择性掺杂区域。对于 GaN,离子注入仍处于起步阶段,需要超过 1 GPa 的压力和 1200 摄氏度以上的温度。

为了解决与离子注入相关的问题,由 Elison Matioli 领导的 EPFL 研究人员已转向 NiO 的射频溅射,NiO 是一种可以实现高空穴密度的 p 型导电氧化物。请注意,在 2020 年,南京大学和中山大学的研究人员都报告了使用掺杂的 NiO 在 Ga2O3 中实现高反向阻断电压,尽管这两种材料之间的带偏移很大。 “这启发我们评估 p-NiO 作为 GaN 功率器件的结终端扩展的使用,”Matioli 说。

他和他的同事并不是第一个报告向 GaN 肖特基势垒二极管添加 p-NiO 结终端扩展的人。今年早些时候,由日本德岛大学研究人员领导的一个团队宣布制造具有这种架构的器件。使用块状 GaN 衬底和 14μm 厚的漂移层,他们实现了低于 250 V 的阻断电压。

较高的阻断电压可能部分是由于从肖特基势垒高度为 0.6 eV 的 TiN 阳极转换为高度为 0.9-1 eV 的镍阳极所致。二极管的设计和制造也可能存在差异。 “我们花费了大量时间来优化结终端扩展的设计、p-NiO 的沉积条件,以及完善我们器件的制造工艺,”Matioli 说。

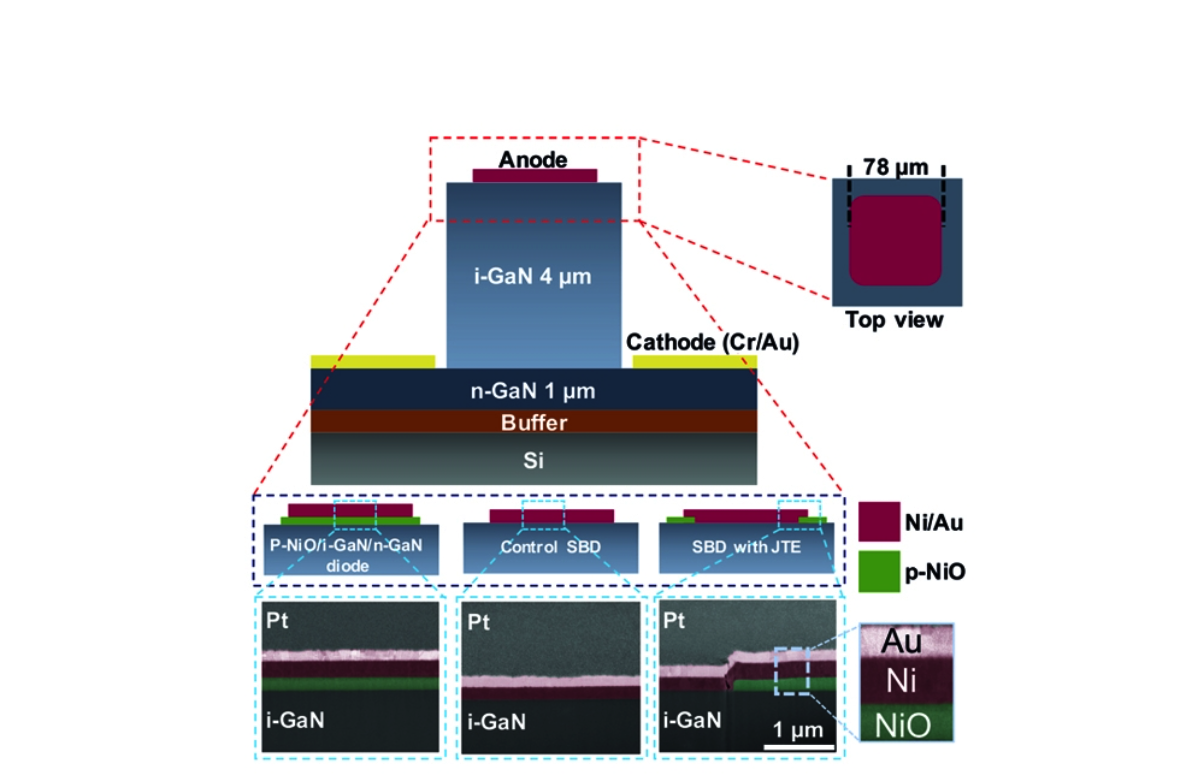

该团队的器件由 Enkris 提供的 150 毫米 GaN 硅外延片制成。这些外延片具有 1.1 µm 厚的缓冲层,然后是 1 µm 厚的 n 型 GaN 层和 4 µm 厚的本征 GaN 层。在 EPFL,工程师通过射频溅射添加了 160 nm 厚的 NiO 层,然后使用剥离工艺来定义结终端扩展区域。为了完成二极管制造,工程师使用 Ni/Au 形成 p 型欧姆接触,然后通过反应离子蚀刻创建台面,从而能够访问 n 型层 - 这有助于添加 Cr/Au 以创建一个n 型欧姆接触。

对作为对照生长的传统 GaN 肖特基势垒二极管和具有结终端扩展的变体的电流-电压测量表明,这种修改对导通电阻或导通电压没有显著影响。然而,阻断电压有大幅增加,从 230 V 上升到 443 V。

该团队的目标是进一步改进其 p-NiO 沉积条件。工作重点将放在射频溅射功率和环境气体通量上,因为这可以减少 p-NiO/GaN 界面的反向泄漏电流。 “这将帮助我们实现各种器件,例如合并 p-i-n 肖特基二极管、结势垒肖特基二极管以及 JFET,”Matioli 说。

上图是生产的二极管的三种变体:一种带有 p-NiO 层,用于研究传输特性;一个控制;和一个肖特基势垒二极管 (SBD),带有结终端扩展 (JTE)。蓝色框中描绘了这些区域的聚焦离子束横截面扫描电子显微镜图像。

参考文献

R. Khadar et al. Appl. Phys. Express 14 071066 (2021)

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

| 上一篇:降低隧道结深紫外 LED ... | 下一篇:柔性 CIGS 的瑞士效率记... |