氧化镓垂直晶体管具有最高的击穿电压

2021/8/15 18:32:47 材料来源:

4.2kV的击穿电压是传统晶体管的1.6倍

新晶科技开发出世界最高击穿电压4.2kV的β-Ga2O3立式晶体管。这比传统晶体管的击穿电压高 1.6 倍。

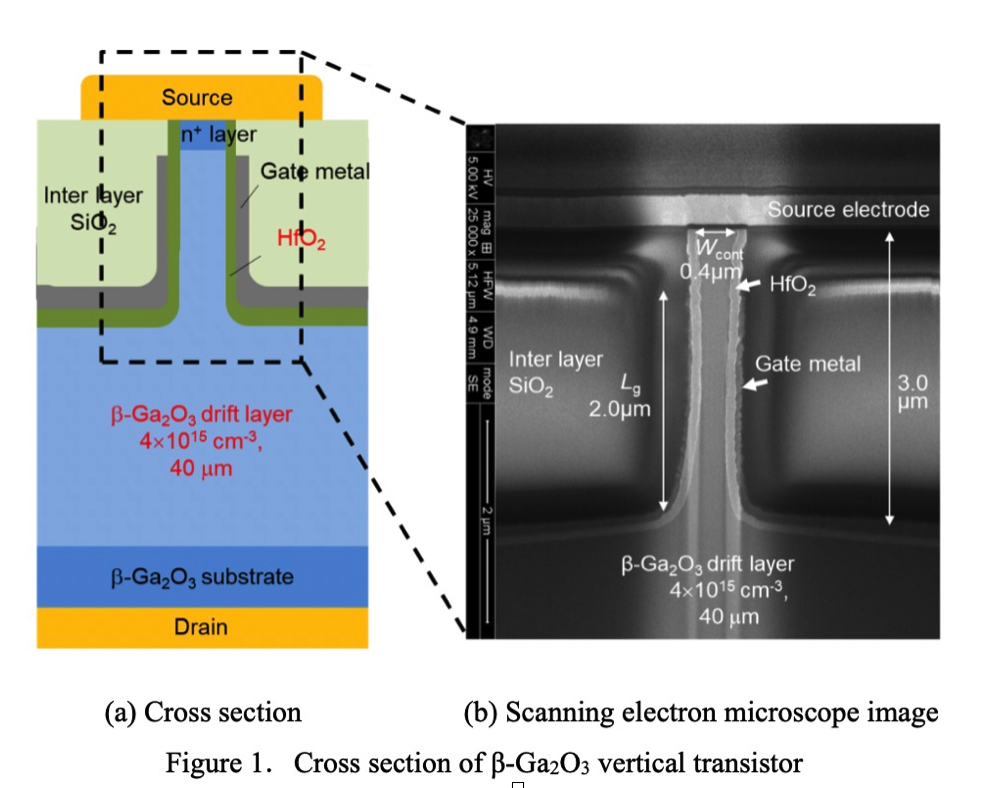

图 1(上图)显示了新开发的 β-Ga2O3 垂直 MOS 晶体管的横截面。

晶体管是一种垂直器件结构,有利于满足功率器件的低损耗和大电流要求。一种 FinFET 结构,通过将台面宽度缩小到亚微米或更小,无需使用 p 型导电层即可实现正常关闭操作。高介电常数氧化铪 (HfO2) 绝缘膜,以削弱栅极绝缘膜中的电场强度。使用我们新开发的高质量厚膜外延生长技术形成的具有低施主浓度 (4 x1015 cm-3) 和厚膜 (40 μm) 的高压漂移层。

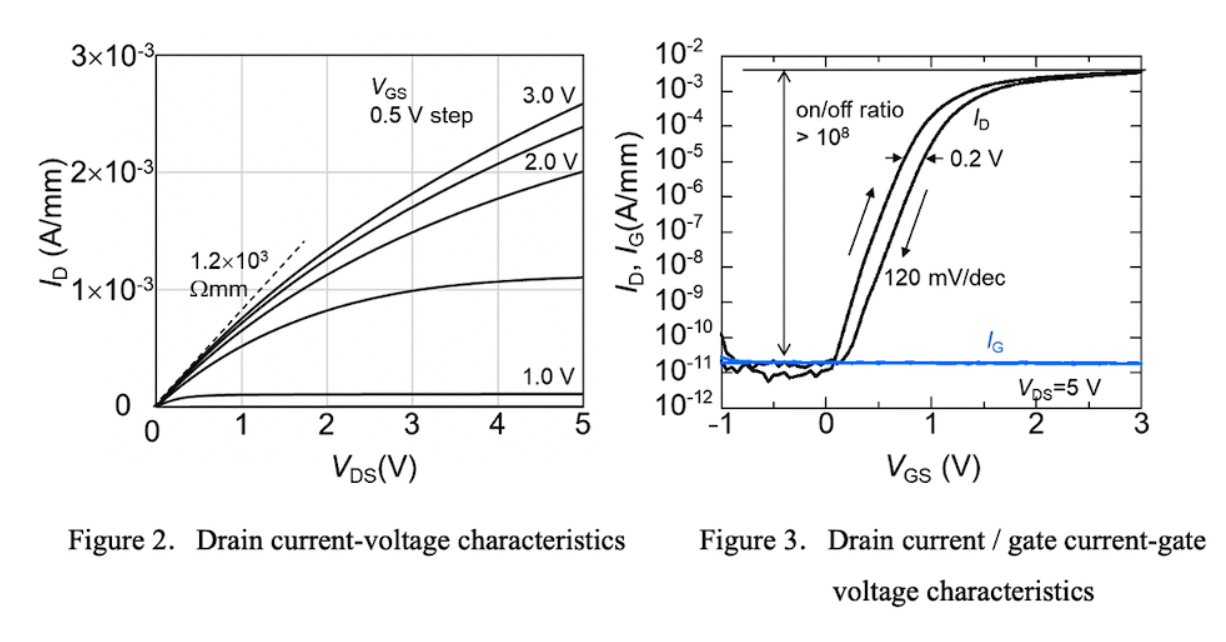

图 2 显示了制作的晶体管(台面宽度 0.4 μm,台面长度 60 μm)的漏极电流-漏极电压特性。该器件显示常关特性,其中在 0 V 栅极电压、最大电流密度为 2.6 mA/mm 和导通电阻为 1.2 x 103 Ω mm 时没有电流流动。在这个晶体管原型中,源极n+层和沟道层相隔约0.4μm,估计源极电阻较高。我们相信通过改进器件设计可以进一步降低导通电阻。

图 3 显示了施加 5V 漏极电压时,漏极电流和栅极电流的栅极电压依赖性。漏极电流开/关比高达8位以上,亚阈值系数9为120 mV/decade,栅极漏电流低于测量限值;从而获得良好的晶体管特性。另一方面,漏极电流-栅极电压特性表现出约0.2 V的滞后,这意味着需要改进MOS栅极界面。

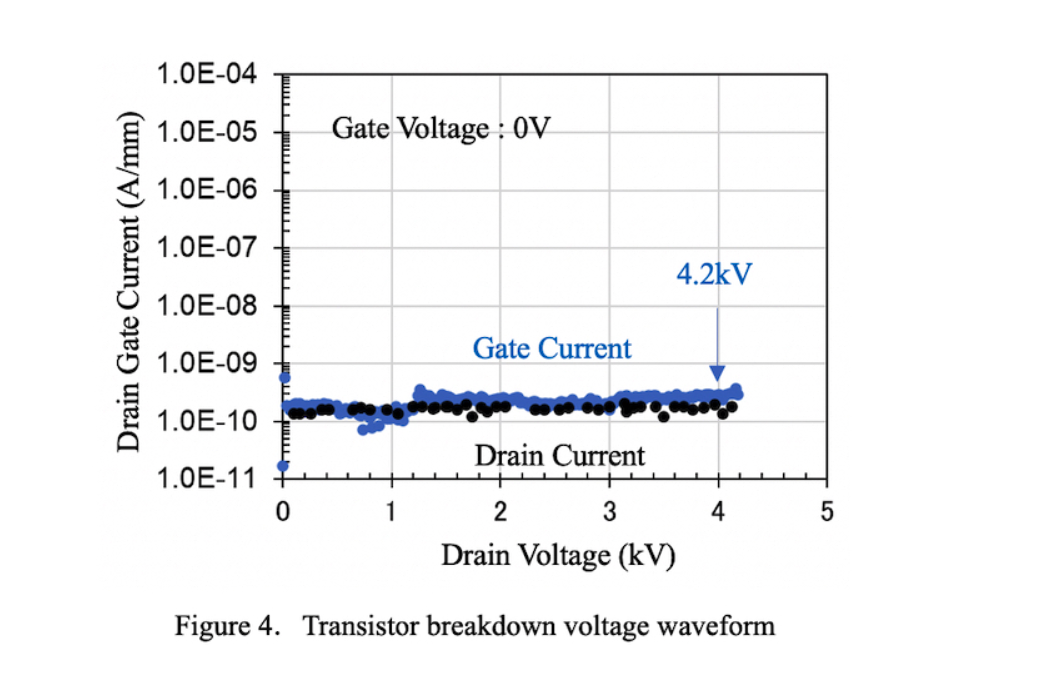

图 4 显示了在栅极电压和源极电压固定为 0 V 的情况下,向漏极施加正电压时的漏极电流和栅极电流特性。 由于 FinFET 结构提供的栅极可控性提高以及台面加工底面的高介电常数HfO2绝缘膜,即使施加高达约4kV的漏电压,也不会产生漏漏电流或栅漏电流。

此外,通过采用低施主浓度(4x1015 cm-3)和40 μm厚膜的优质外延层作为漂移层,击穿电压为4.2 kV(之前报道的2.6 kV值的1.6倍) (W. Li et al., IEDM 19-270))。

台面加工底面上的 β-Ga2O3 漂移层中的最大电场强度估计为 2.5 MV/cm。二维器件模拟表明,在栅电极端产生了比这强几倍的电场浓度。因此,将来可以通过引入减轻电场集中的电极终端结构来进一步提高击穿电压。我们相信可以实现低导通电阻。

未来发展

除了解决通过研究该器件原型澄清的问题外,研究团队还将努力增加器件的尺寸和电流。 2025年开始量产600-1200V中击穿电压器件,为3000V及以上高击穿电压器件量产做准备。

用于中击穿电压区域的 β-Ga2O3 半导体的低成本是电动汽车和其他商业应用的优势。我们将继续发展以达到我们的目标。

声明:本篇文章属于原创,拒绝转载,如果需要转载,请联系我们,联系电话:0755-25988571。

| 上一篇:诺森比亚大学投资开发O... | 下一篇:科学家开发出高效的基于... |