更好晶面的 SiC MOSFET

2020/10/10 13:23:33 材料来源:CSC

具有V形沟槽的SiC MOSFET可降低导通电阻并减小开关损耗。

作者:Kosuke Uchida, Takashi Tsuno; 住友电工株式会社

2020年1月份世界上几个最强大国家的领导人召开了世界经济论坛,其中的一个主要议程主题就是气候变化。对于他们这些人来说,这是迄今为止我们这个时代最大的问题,现在就需要马上采取行动减少碳足迹。

现在还有很多机会可以保证去做到这一点。有些是国家层面的,比如增加核电厂和太阳能发电厂的数量。还有些是公司可以做出的一些改变,例如投资更高效的机器,当然也有一些纯属个人的决定,例如转向以植物为基础的饮食,减少坐飞机航行等。

在这种组合中,节省能源和减少二氧化碳排放的一种选择是引入更有效的功率控制技术。功率控制技术部署广泛,在电动汽车,可再生能源系统和工业电机驱动中起着至关重要的作用。

当今大多数功率器件都是由硅制成的。几十年来,它们的性能有所提高,但是现在它们已经突破了根据其物理性能计算得出的理论极限。这意味着不再可能显著降低由于传导和开关损耗而引起的功率损耗。

目前需要的是用宽带隙材料(例如SiC和GaN)制成的器件来代替硅器件。这两种材料非常引人注目,是因为它们在许多方面都具有领先于硅的优势,包括更高的介电击穿电场,更高的电子饱和速度和更高的导热率。由于这些特性,SiC和GaN可以提供更高的击穿电压和更低的导通电阻,从而可以降低传导损耗。

SiC和GaN之间值得注意的区别是晶体的质量。体SiC材料具有较少的晶体缺陷,因此可以制造高质量的SiC外延衬底,进而可以生产垂直SiC功率器件。这些使用整个外延层表面的器件将高电流与600V或更高的击穿电压结合在一起。因此,SiC有望在实现高功率的高压应用中取得最大的成功,而GaN有望用于低输出功率的应用。

SiC器件将取代硅绝缘栅双极晶体管(IGBT),该晶体管结合了高击穿电压和低电阻。由于该器件的双极性工作,开关损耗随电子-空穴复合时间的增加而增加。SiC MOSFET则不会如此,因为SiC MOSFET是一种单极性器件,可提供高速开关和更高的击穿电压。

卓越的沟槽

在日本住友电气工业有限公司,我们为SiC MOSFET开发了一种新的架构。它具有V型沟槽,使我们能够利用具有更高迁移率的材料性能。

这个开发过程是可以借鉴我们在 产品生产方面的丰富经验,其中包括GaN HEMT,GaAs FET以及构成其基础的衬底。最近,我们一直在开发SiC晶体,并开始大规模生产6英寸SiC外延衬底,我们将其称为EpiEra。它们是使用高质量,具有成本效益的生长技术生产的——我们将其称为我们的多参数和区域控制的SiC生长技术。我们使用独特的仿真技术来确定最合适的掺杂浓度均匀性,以实现预期的器件性能和良率。通过垂直整合SiC的材料和器件技术,我们生产出了高性能和高良率的SiC MOSFET。

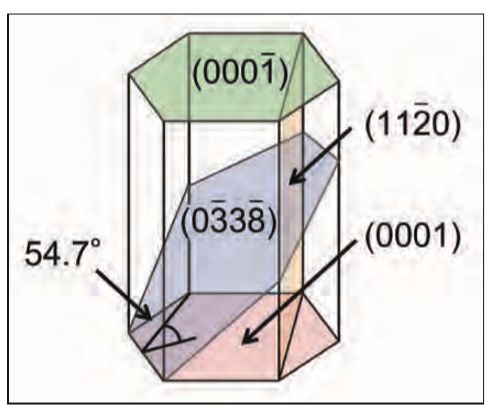

我们之所以开发出新颖的MOSFET架构,是因为由于界面状态密度高,传统设计中的沟道迁移率将会大大低于材料的体迁移率。为了演示我们可以实现的目标,我们在4H-SiC( )面上制造了一个横向的MOSFET,该面与(0001)面成54.7度的偏角(见图1)。

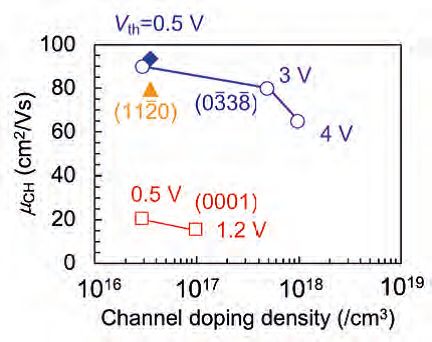

我们的结果表明,这是制造SiC MOSFET的最佳晶面,这是因为由于其较低的界面态密度和较高的自由电子比,该面在所有掺杂浓度下的沟道迁移率最高。(见图2)。当采用1018/cm3的掺杂浓度时,可实现60cm2V-1s-1的高沟道迁移率,以及高达4V的阈值电压——该电压足以抑制高温下的误启动。

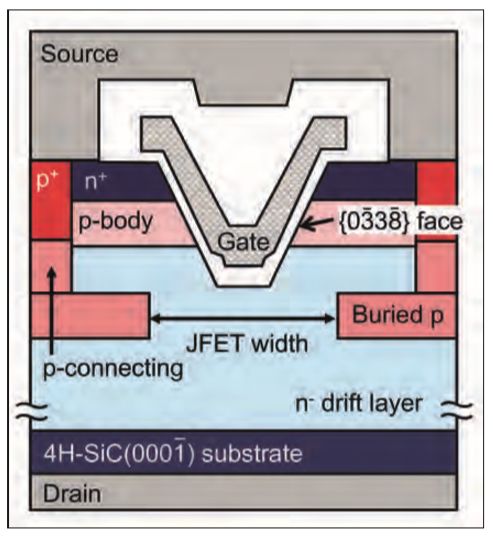

为了充分利用这个晶面的优势,在过去的几年中,我们开发并商业化了4H-SiC V形沟槽MOSFET,该器件被称为VMOSFET。最近,我们已经在致力于提高功率转换效率,从而使得这些器件能够处理数百安培的电流,并且击穿电压高于1kV。这些晶体管具有4H-SiC{ }沟槽侧壁,该侧壁具有比其他SiC晶面更高的沟道迁移率(此结构的示意图请参见图3)。使用这种设计,可以在实现高沟道密度的同时降低沟道电阻。

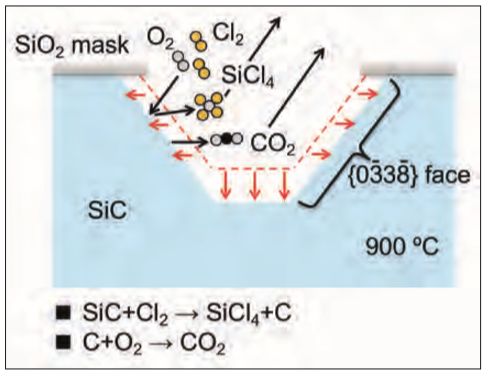

生产该器件的关键是使用化学刻蚀工艺来形成V形沟槽。我们使用二氧化硅作为刻蚀掩模,并在约900℃的氯气环境中进行刻蚀。在此工艺中,氯气在表面产生化学反应,使得SiC转化为碳,然后再与氧反应。生成的氯化硅和二氧化碳在高温下蒸发(见图4)。

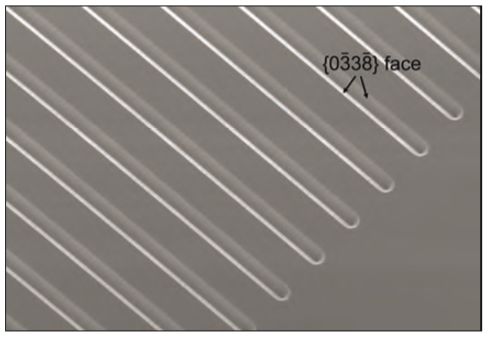

此工艺将会导致{ }面暴露出来,而这些面是非常稳定的。注意,利用诸如反应离子之类的刻蚀,是形成U形沟槽的常规方法,但是将会导致刻蚀损坏和子沟槽的形成。通过扫描电子显微镜的图像,我们可以看到采用我们的方法获得了高质量的晶面(见图5)。

沟槽结构的缺点是当向器件施加高电压时,在沟槽底部形成的栅极氧化膜容易击穿。发生这种情况时,电场集中在栅极氧化膜上。为了解决这个问题并增强VMOSFET的可靠性,我们在沟槽底部周围注入p型电场缓冲区。借助于此额外的区域,施加到漏极的高电压会使得电场集中在掩埋的p区边缘上。采取这样的改善措施减轻了栅极氧化膜上的电场。

通过这种设计,我们能够通过减小栅极和漏极之间的寄生电容,从而提高了开关速度并减少了开关损耗。这通过电学连接掩埋的p区到具有p连接区域的源极,从而形成源极电势来得以实现。

验证的可靠性

为了确保实现长期可靠性的低导通电阻和低氧化物电场,至关重要的是优化JFET的宽度和掩埋p区之间的宽度。我们与此相关的工作包括研究漏极偏置条件下,氧化物电场与寿命之间的关系。

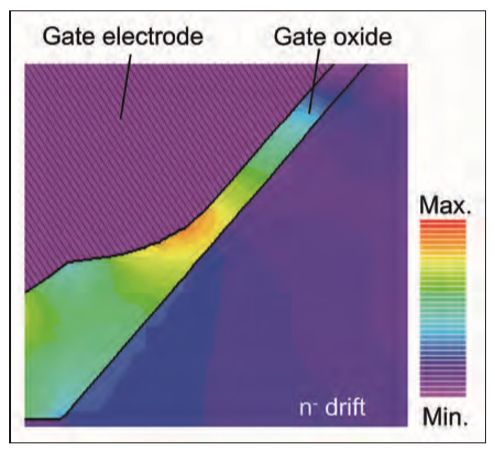

使用具有专用结构的测试芯片,我们获得了高温反向偏压条件下的寿命估值。为了增加氧化物的电场,相比为大规模生产而设计的VMOSFET,这里具有V槽栅极沟槽结构的管芯具有较大的JFET宽度。这些测试是在175℃的环境温度下进行的。这些晶体管中的氧化物电场已使用Technology CAD模拟计算得出。电场分布的计算表明,由于电场拥堵,氧化物电场在底部氧化物边缘具有最高点(请参见图6)。

进行高温反向偏置测试后,我们分析了VMOSFET的失效点。我们发现其位置对应于我们模拟出来的氧化物电场的最高点。

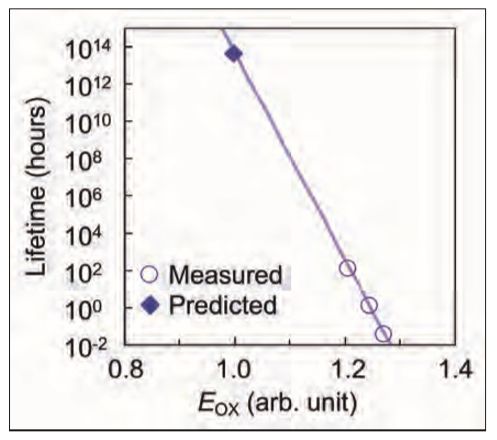

通过这些测量,我们确定了氧化物电场对寿命的影响。图7显示了10%累积故障率的图表。

对于高可靠性应用,我们的目标是累积故障率为百万分之0.1时,寿命达20年以上。我们的结果大大超出了这个值。对于1.0的氧化物电场,请注意这里采用的是任意单位,预测寿命为4.5×1013小时。根据我们将寿命与累积故障率相关联的计算,这等价于在0.1ppm累积故障率条件下,可以达到200年的寿命。

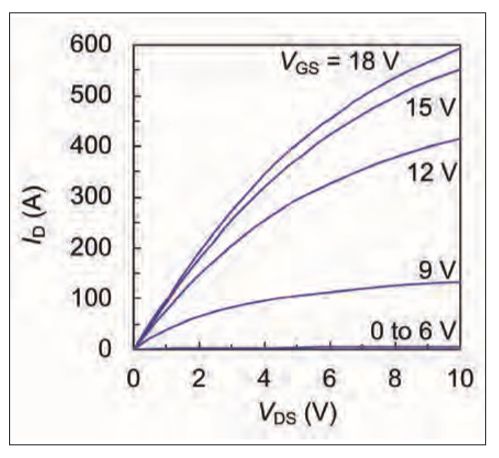

利用高温反向偏置测试的结果,我们使用仿真设计了一种结构,该结构具有低导通电阻,并且在1200V的漏极偏置下有1.0的氧化物电场。这让我们得以在150毫米晶圆上,制造出具有优化设计的VMOSFET。在结温为25℃的条件下工作时,制造的6.0平方毫米管芯可以处理200A的直流电流和高达600A的脉冲电流(见图8)。栅极-源极电压为15V且漏极-源极电压为1V时,比导通电阻仅为3.1mΩ cm2;在25℃,当漏极-源极电压等于栅极-源极电压时,阈值电压为4.6V,而漏极电流密度为1mA/mm2。

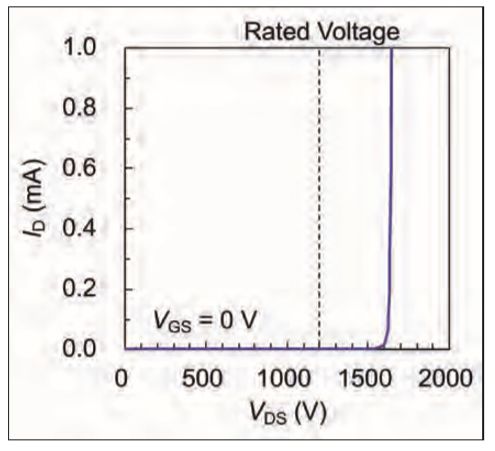

击穿电压远高于目标值,能够承受高达1640V的电压(见图9)。另一个令人鼓舞的特性是栅极到漏极的电容很小——漏极-源极电压为800V时仅为15pF,由于接地的p区有效地阻塞了来自漏极的电力线,因此让我们能够有效抑制自导通。

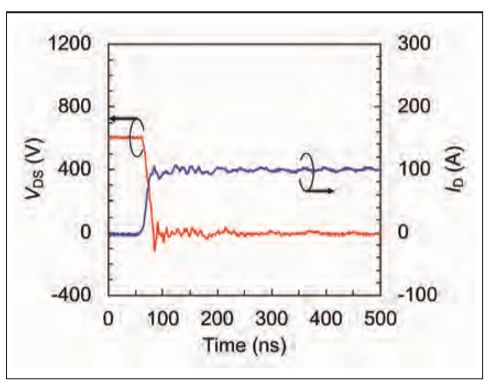

我们还采用电感负载进行了双脉冲测试,其中使用SiC肖特基势垒二极管作为自由轮器件(详细信息请参见图10)。该测试展示出我们的VMOSFET的快速开关速度和低开关损耗。上升和下降时间分别为16ns和7ns;导通和关断能量损耗仅为260μJ和270μJ,因此总开关损耗仅为530μJ。

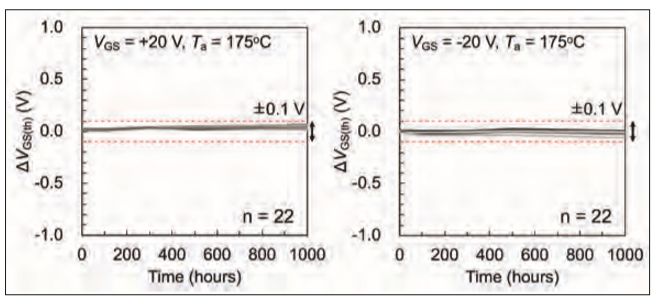

进一步的测试涉及评估我们的VMOSFET的阈值电压稳定性。175℃下评估了22个样品后发现,经过1000小时的高温栅极偏置测试,其阈值电压漂移小于0.1V。这个小的偏移也再次证明了{ }晶面上栅极氧化物的稳定性和高质量。

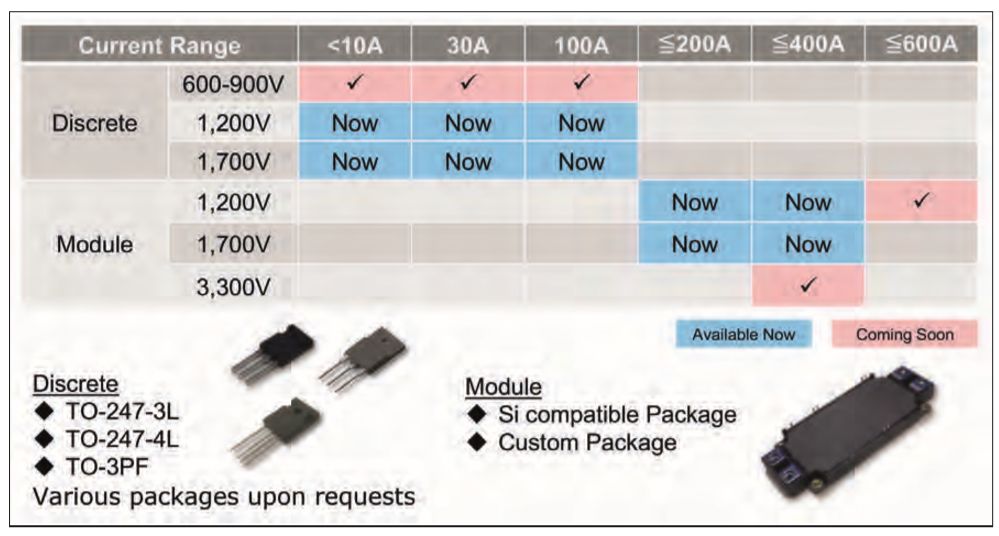

我们1200V/200A VMOSFET的成功开发,使得我们能够扩展此类晶体管的产品线阵容(请参见表1)。从用户的角度来看,采用VMOSFET可以实现:在组件和系统级都具有更好的性能;设计更小组件的能力更强;稳定的供应链和更好的质量管理。我们预计,我们结合低功耗和高可靠性的VMOSFET的卓越特性,将为SiC市场的进一步拓展奠定基础。

本研发工作的部分支持来自超级洁净室电力电子生产线(SPEL)的联合研究财团项目,主持单位为国家先进工业科学技术研究所。

扩展阅读

K. Wada et al. Mater. Sci. Forum 105-108 963 (2019)

T. Hiyoshi et al. Mater. Sci. Forum 740-742 506509 (2013)

T. Hatakeyama et al. Appl. Phys. Express 12 021003 (2019)

图1. 4H-SiC的主要晶面。( )面与(0001)面的夹角为54.7度。

图2. SiC横向MOSFET的沟道迁移率与掺杂密度的依赖关系。( )面显示出比其他晶面更高的沟道迁移率和更高的阈值电压。

图3. SiC VMOSFET的剖视图。

图5. V型槽的扫描电子显微镜(SEM)图像。

图6. 通过TCAD技术计算出的V形沟槽底部周围的电场分布,用于进行寿命估算。

图7. VMOSFET的长使用寿命。累积故障率为10%,T=175℃,漏极偏置条件情况下所估算的寿命。在0.1 ppm累积故障率的条件下,预计寿命等于200年。

图8. T=25℃时,ID-VDS特性(VGS=0 – 18V)。VMOSFET展示出200A DC和600A脉冲的高电流能力。

图9. 阻断特性。VMOSFET对1200V的额定阻断电压显示出足够的余量。

表1. 住友电气工业株式会社的VMOSFET产品阵容。

图10. 双脉冲测试下VMOSFET的快速开关特性。该测试的条件是:RG=1.0Ω,VGS=+15/-5V,VDD=600V,ID=100A,L=100μH。

图11. 在T=175℃,VGS=+20V(左)和-20V(右)的高温栅极偏置测试下,VMOSFET的稳定阈值电压。

| 上一篇:使用高性能特种聚合物优... | 下一篇:为什么选择GaN晶体管?... |