绝缘插入层大幅提高击穿电压

2020/7/29 10:32:15 材料来源:CSC

当在氮化镓和硅之间插入绝缘体时,GaN-on-Silicon HEMT可以突破外延层所能承受的击穿电压极限。

作者:

Zhihong Liu, Hanlin Xie,Kwang Hong Lee,新加坡-麻省理工学院研究和技术联盟

Chuan Seng Tan, Geok Ing Ng,南洋理工大学

Eugene Fitzgerald, 麻省理工学院

GaN具有很多优异的特性,包括宽带隙,相当大的临界电场,以及极化诱导的高密度二维电子气。这些品质是高性能GaN HEMT背后的根本原因。这种晶体管的性能优于用硅制成的对标产品,并能够实现构建兼具低功耗,高功率转换效率和高工作频率的功率转换器。

为了使GaN功率二极管和晶体管相比基于硅的功率二极管和晶体管更具竞争力,这些产品的成本必须降低。一种有前途的选择是用200毫米硅基氮化镓(GaN-on-Silicon)晶圆制造这些器件,因为这可以降低衬底成本,并在成熟的硅代工厂实现大批量生产。目前这方面已经取得了很大的进展,其中包括采用200mm硅基氮化镓外延晶圆进行这些宽带隙HEMT的商业化生产。

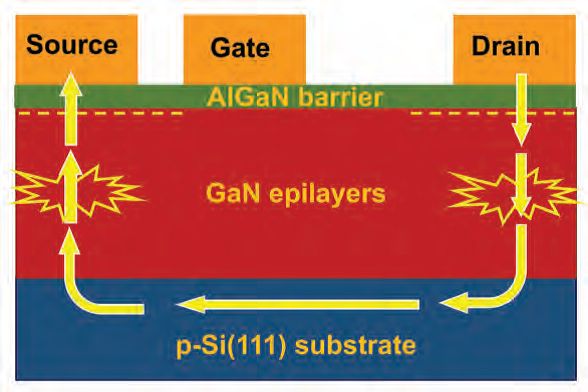

然而,针对现有技术,存在与晶体管的击穿电压有关的担忧。像其他横向功率器件一样,HEMT的击穿电压随其栅极到漏极距离的增加而增加。以此为基础,松下公司的一个团队利用125μm的栅极到漏极的距离,实现了超过10kV的击穿电压。但是,这项创纪录的壮举采用的衬底不是硅,而是蓝宝石。这是一个很好的选择,和选择SiC一样,因为它可以扩大栅极到漏极的距离,从而提高阻断电压。对于硅而言,情况却并非如此,这是由于GaN外延层的垂直击穿会导致泄漏电流流过导电的硅衬底(参见图1)。因此,对于这种硅基氮化镓的材料组合,最大的可获得击穿电压取决于GaN外延层的厚度。

图1. 当常规的硅上GaN HEMT中的GaN外延层垂直击穿后,电流会流过导电的硅衬底。

为了尝试增加 GaN-on-Silicon HEMT的击穿电压,人们已经进行了很多努力来改进生长技术,以使得硅衬底上的氮化镓缓冲层更厚。但是由于晶圆龟裂、翘曲甚至断裂等严重问题,实现这一目标绝非易事。所有这些都是由于硅衬底和GaN外延层之间存在较大的晶格失配和较大的热膨胀系数差异而产生。这些差异对大尺寸晶圆(例如直径为200mm的晶圆)产生了巨大的影响。对于这种尺寸的晶圆, GaN HEMT的击穿电压直到最近都一直被限制在1900V以下,最好的结果来自具有4.5μm的GaN外延层厚度的结构。

研究人员已经开发了若干种技术来尝试克服这些限制。在麻省理工学院,Tomas Palacios的团队已经将GaN HEMT外延层从硅衬底转移到玻璃上,以试图提高横向器件的击穿电压。这带来了好处,将击穿电压从大约600V增加到了1.5kV,并且提供了实验证明,证明硅衬底是导致栅极到漏极距离超过一定值的HEMT击穿电压饱和的根本原因。但是,改用玻璃不是一个很好的解决方案,玻璃的导热系数很低,并且与硅CMOS代工厂不兼容。

其他研究小组已通过局部去除硅衬底获得了某些成功。这个想法由imec的Puneet Srivastava及其同事提出,并由IEMN的Farid Medjoub的小组实施,实现了3kV的击穿电压。

同样,这个胜利也是要付出代价的。在这种情况下,对于大面积功率器件和大尺寸硅基GaN晶圆,去除衬底都会导致机械稳定性方面的问题。另外,热扩散也受到损害,部分硅衬底的损失限制了热扩散的路径,导致了热阻的增加。

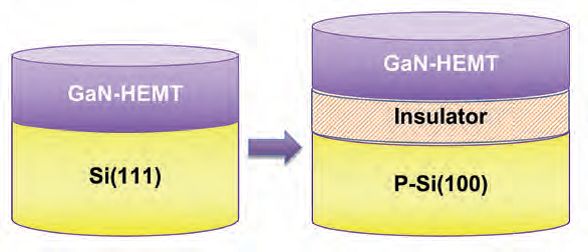

为了避免与使用玻璃或去除衬底相关的问题,新加坡-麻省理工学院研究与技术联盟(Singapore-MIT Research and Technology Alliance),南洋理工大学和麻省理工学院的团队正在率先开发一种不同的方法,使用硅上绝缘体上氮化镓(GaN-on-insulator (GNOI)-onsilicon)的结构(请参见图2)。我们的新颖架构在VLSI Symposium 2019上首次亮相,通过使用晶圆键合在硅衬底和器件层之间插入附加的绝缘体,避免了对厚GaN外延层的需求。

我们的方法具有许多优势。使用大面积的硅晶圆,我们可以在硅代工厂中加工材料;我们可以去除因为许多位错和较差的导热性而使性能受限的原始过渡层,从而提高器件的可靠性和散热能力;在高温GaN生长之后,我们可以用一种具有良好硬度的新衬底,来替换原来的易碎硅衬底,这可以降低晶圆通过产线时破裂的可能性,从而提高良率。

插入绝缘体

我们的新型HEMT的制造始于准备200mm GaN-on-silicon(111)晶圆和硅支撑基板。在化学机械抛光降低表面粗糙度之前,在它们的正面都沉积SiO2,然后将该氧化物致密化。之后,清洗表面,使用等离子活化处理,然后键合在一起。随后使用高温退火来强化这种键合。

为了能够插入绝缘体,去除了用于生长GaN外延层的原始硅(111)衬底。这将暴露出GaN外延层的背面(在我们的情况下,为N极性面),以便可以将其键合到新的p型硅(100)衬底上。与第一次的键合工艺相似,在经过SiO2沉积,致密化,化学机械抛光和表面活化之后,将硅上GaN支撑晶圆和新的p型硅(100)晶圆键合在一起。最后,去除硅支撑衬底和键合材料,以露出GaN前表面(Ga极性面),并实现硅上GNOI晶圆(参见图2)。

图2. 硅上绝缘体上氮化镓(GNOI)晶圆,可以突破由于GaN外延层垂直击穿引起的击穿电压极限。这是通过在GaN外延层和硅衬底之间添加绝缘层,从而提高垂直击穿电压来实现的。

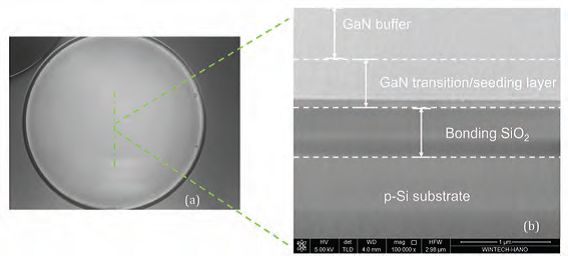

图3.(a)所制备GNOI晶圆的红外透射图像。没有形成明显的气泡。(b)GNOI晶圆横截面的扫描电子显微镜图像。

我们已经通过多种技术仔细检查了异质结构的材料质量。我们的200mm硅上GNOI晶圆的红外透射图像显示,键合界面处没有可见的气泡(见图3(a)),扫描电子显微镜显示GaN,SiO2和硅之间存在清晰的界面。

根据霍尔测量,材料的二维电子气的密度和迁移率分别为8.7×1012cm-2和1930cm2V-1s-1。将这些值与硅上GaN结构的值进行比较,表明我们生产硅上GaNOI晶圆的工艺不会影响GaN异质结构的电学特性。

评估性能

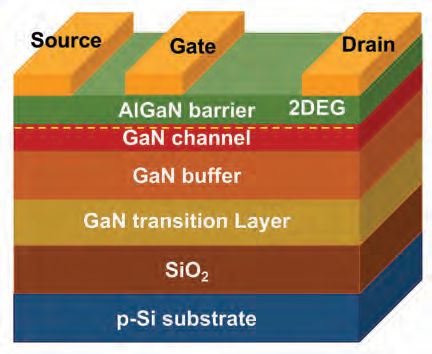

为了查看我们的GNOI架构是否能够实现期待的性能,我们用一小块的200mm硅上GaNOI晶圆制造了GaN HEMT(有关我们的GaN HEMT结构,请参见图4示意图)。我们使用GaN HEMT的标准制造工艺流程形成了这些晶体管。在通过台面等离子体蚀刻实现器件隔离之后,我们使用Ti/Al/Ni/Au金属叠层,并在775°C下进行退火,从而实现了欧姆接触。测量表明,欧姆接触电阻为0.5-0.7Ω-mm。制造这些晶体管的最后步骤是制备肖特基栅极接触,该接触采用Ni/Au金属体系,并在氮气气氛中400°C下进行10分钟的栅极后退火工艺来实现。请注意,这些器件中没有使用场板。为了对其进行基准测试,我们还用一块200mm的硅上GaN晶圆制成了GaN HEMT,采用的是完全一样的工艺。

图4. 在硅上GNOI晶圆上所制作的HEMT。

使用众所周知的FATFET技术进行测量,揭示了两种类项HEMT的2DEG漂移迁移率。插入绝缘体没有产生明显影响,两种类型晶体管的迁移率都在1900-2100cm2V-1s-1范围内。

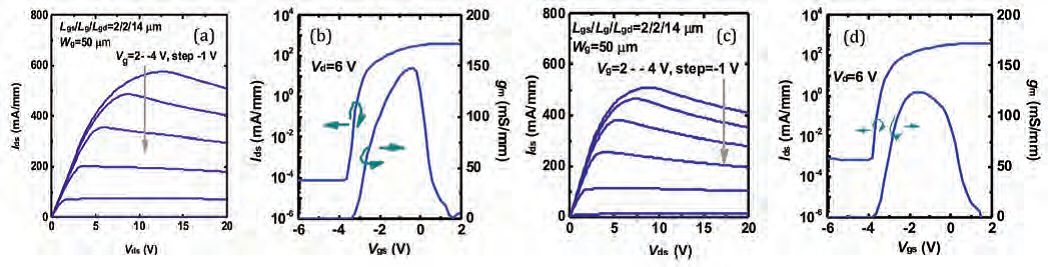

我们还测量了两种类型HEMT的直流特性,考虑了栅源间距为2μm,栅长为2μm,栅漏距离为14μm的器件。如图5所示,对于硅上GNOI器件,最大漏极电流为508mA/mm,导通电阻为8.8Ωmm,最大跨导峰值为140mS/mm,阈值电压为-2.85V。对于硅上GaN类型,数值仅略有不同,对应数字为576mA/mm,11.0Ωmm,147mS/mm和-2.37V。

图5. Lgs/Lg/Lgd=2/2/14μm的硅衬底上GaN HEMT的(a)输出(Id-Vd)和(b)转移(Id-Vg)特性;Lgs/Lg/Lgd=2/2/14μm的硅衬底上GNOI上HEMT的(c)输出(Id-Vd)和(d)转移(Id-Vg)特性。

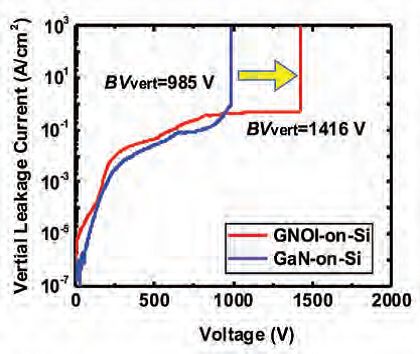

将硅基板接地,并将正偏压施加到在顶部AlGaN/GaN异质结构上制造欧姆接触上之后,我们测量了垂直击穿电压(请参见图6,可以看到不同偏压下的垂直泄漏电流图)。硅上GNOI晶圆的垂直击穿电压为1416V,相比硅上GaN晶圆,这提高了约430V。

图6. 采用衬底接地,硅上GNOI和硅上GaN晶圆上欧姆接触焊盘的垂直泄露电流与偏置电压的关系。

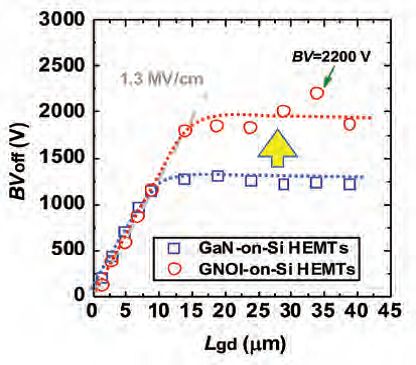

在衬底“悬浮”的情况下,我们测量了三端断开状态下的击穿特性(见图7)。关态击穿电压定义为,在1mA/mm时即发生硬击穿时的值。曲线清楚地表明,随着栅极到漏极距离的增加,击穿电压首先增加,随后饱和,对于硅上GNOI HEMT,平台开从14微米时开始,而对于控制器件,则从9微米处就开始了。失效的原因是GaN外延层和/或SiO2的垂直击穿,以及流过导电硅衬底的电流的综合作用。

图7.(a)硅上GaN晶圆,(b)硅上GNOI晶圆上具有不同栅-漏长度器件的三端截止状态击穿特性。衬底是悬浮的。击穿电压(BVoff)定义为Ids=1mA/mm时。

将绝缘体插入GaN和硅衬底之间,可以大大改善击穿电压。它增加了约700V,达到约2kV。对于栅极至漏极距离为35微米的器件,最大击穿电压可高达2200V。

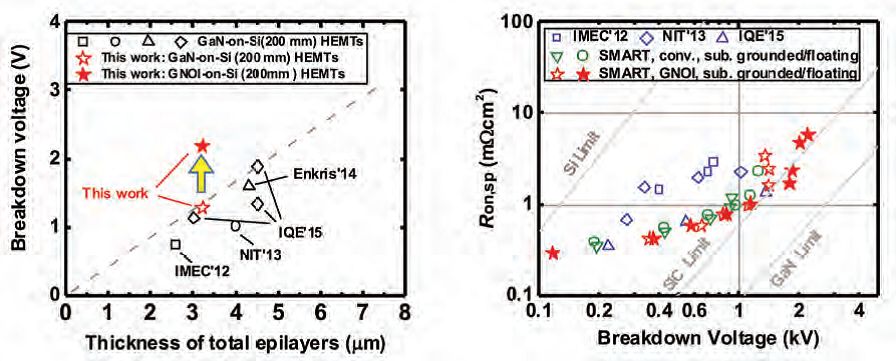

我们已经对我们的器件进行了基准测试,根据GaN外延层的总厚度对它们进行了比较,并与其他200mm硅上GaN晶圆制成的HEMT的报告进行了比较。我们最高的2.2kV击穿电压达到新的高度,超过了IQE先前报道使用了4.5微米 GaN外延层的1900V记录(见图8)。这些数字实际上低估了绝缘体带来的好处。比较相同外延层厚度(即3.2微米)的结果,使用GNOI结构的击穿电压就会高出900V。

另一个重要的考虑因素是比较导通电阻及其与击穿电压的关系。同样,我们的器件正在提升可能的高度(参见图8(b))。对于由200mm硅上GaN晶圆制成的HEMT,其优值达到创纪录的1.87GW/cm2。

图8.(a)最新最高的200mm硅上GaN晶圆BVoff与GaN外延层总厚度的关系。(b)报告200mm GaN晶圆上HEMT的Ron, sp作为BVoff的函数。该项工作中,FOM(BV2/Ron, sp)值达到了创纪录的1.87GW/cm2。

热问题的解决方案

我们的硅上GNOI晶圆的一个弱点,是提供晶圆键合绝缘体的SiO2层的导热性差。为了评估绝缘层对器件热性能的影响,我们使用Silvaco TCAD工具进行了电热仿真。在这项工作中,我们对AlGaN势垒使用了0.3W/cm-K的热导率值,对于GaN缓冲层使用1.6×(300/T)1.4W/cm-K的热导率值,对于GaN过渡层使用了0.1W/cm-K的热导率值,SiO2键合材料为0.012W/cm-K,硅衬底为1.48×(300/T)1.65W/cm-K。

为了进一步提高硅上GNOI晶圆制成的HEMT的性能,其选择包括采用在这方面更出色的某种材料来替代低导热率的SiO2键合材料。候选材料包括AlN和多晶金刚石。

为了评估这些材料的优势,我们进行了仿真,对于700nm AlN的热导率,使用1.13W/cm-K的热导率,对于700nm多晶金刚石,采用值为2.3W/cm-K。根据计算,加入AlN键合材料或多晶金刚石键合材料会将器件的热阻从45°C(W/mm)减小到29°C(W/mm)。

出色的热管理是获得更高功率的关键。如果沟道温度必须不能超过150°C,则硅上GNOI晶圆的允许功率从使用SiO2键合材料的3.9W/mm可以增加到使用AlN键合材料的5.3W/mm,而使用多晶金刚石键合材料的则达到5.4W/mm。这是一项重大的改进,表明可以用AlN或多晶金刚石解决由于SiO2键合材料产生的热问题。

简而言之,很明显,将新材料引入硅上氮化镓HEMT可以改善这种晶体管的性能。插入SiO2将击穿电压提高到新的高度,并改善了其他品质因数;同时添加导热率比SiO2高的键合材料可防止对热管理造成任何的损害。这表明我们可以实现功率更高的HEMT,同时又能够控制使其保持低热状态。

扩展阅读

Z. Liu et al. Proc. of VLSI tech., 2019

B. Lu et al. IEEE Electron. Dev. Lett. 31 951 (2010)

E. A. Fitzgerald et al. ECS Trans. 75 31 (2016)

Y. Zhang et al. IEEE Tran. Electron Dev. 602224(2013)

| 上一篇:宽禁带生态系统:快速开... | 下一篇:GaN将能源效率推升至新... |