新型热原子层刻蚀技术制造创纪录性能的极小型 InGaAs FinFET

2020/5/12 13:08:15 材料来源:CSC

作者:Wenjie Lu, Younghee Lee, Jesús Del Alamo, Steven George;

麻省理工学院和科罗拉多大学博尔德分校

过去的五十年,硅基CMOS的尺度缩小驱动着微电子技术的革命。随着器件尺寸的缩小,晶体管的性能不断提高,很好地维持了摩尔定律。目前的问题是,这种情况还能持续多久?

整个20世纪,CMOS技术的进步来自于平面晶体管尺寸的缩小。但最近,CMOS的设计思路已发生了改变。调整包括了三维结构的引入,这给生产带来了严峻的新挑战,特别是在最新的例如FinFET的硅基多栅极晶体管的制造中,新挑战的解决显得尤为重要。这类新型晶体管的尺寸大小已经达到了低于10 nm的水平——例如,最新的Intel 10 nm FinFET的鳍片仅具有7 nm宽。

如此小型化是人类在技术发展上的非凡一步,这甚至在十年前都是无法想象的。这不仅是简单地减小FinFET宽度——同时为了满足高电流密度需求,鳍片还必须足够高,如此虽然可以满足性能指标,但结构非常脆弱。

现代FinFET器件的另一个特性是其表面积决定了其性能,要确保其正常工作,就必须具有高质量的MOS接口。 为了实现伴随尺度持续缩小的这个需求,刻蚀技术必须能够支持亚纳米级的精度和准确度,同时又能制备高度完美的界面,这是当今主流刻蚀方法无法企及的。

热原子层刻蚀

在硅晶圆厂中,图案化微米级和纳米级结构的最常见方法是等离子刻蚀。 自1970年代开始使用以来,CMOS制造中的这一基本制造技术,已经发展得越来越完善。但是,这项技术也只是止步于此。新的刻蚀技术需要具有更高的环境友好性和多功能性,同时能实现亚单层刻蚀控制,以满足晶圆厂生产10纳米以下的3D结构晶圆的需求。

近来,一种新刻蚀技术引起了人们的广泛关注。原子层刻蚀技术,或简称为ALE,是当今最先进的刻蚀技术。该技术实质上是原子层沉积(ALD)的逆过程,基于两个自限性过程:通过反应物质修改器件表面;然后,选择性地刻蚀修改过的表面,保留下面未接触的基底。

ALE可以细分为两种类型。一种更通常熟知为等离子体原子层刻蚀技术,在过去几年已经取得了很大的进展,涉及利用反应性等离子体例如Cl2等离子体对表面进行修改,然后将高能的离子或中性粒子例如氩等离子体引入腔室来进行刻蚀。这种刻蚀技术是各向异性的——即有方向性——在很多图案转移中的有实用属性。

另一种是热原子层刻蚀技术。它不用等离子体,而是替代性地通过化学配体交换过程去除材料。其反应过程非常相似于原子层沉积,即通过将化学前体脉冲引入反应器中以完成两个独立的自限步骤。与ALD技术相似,热原子层刻蚀是各向同性的过程。热ALE技术比等离子ALE技术要年轻得多,2015年被首次提出,被用于刻蚀Al2O3薄膜。从提出至今,该技术的大多数报道都局限于刻蚀电介质、金属和氮化物薄膜等材料。没有器件级的阐述。

III-V型 刻蚀

我们与MIT-University of Colorado的合作以弥补对这项技术研究的空缺,使用热ALE工艺来制造晶体管。我们最初的努力指向是开发一种热原子层刻蚀技术来刻蚀III-V族 ,特别是InGaAs材料。

我们聚焦这种三元材料,是因为它在CMOS逻辑和射频应用方面有应用前景。其优点包括有非常高的电子速度,在更低工作电压下比传统硅基MOSFET实现高性能。最近,这种器件正在迅速发展,我们2017年阐述了InGaAs基 FinFET的鳍片宽度已经低至7 nm。

但是,直到2018年前后,我们实验获得的InGaAs FinFET的性能仍与预想中的相去甚远,这主要是MOS接口质量较差造成的。

在深入探究我们的工作详情之前,我们想先指出ALD的引入对III-V晶体管的性能产生了巨大影响。在十年前,这种沉积技术就已被引入III-V族MOSFET工艺。由于自清洁效应,这项技术有助于减轻氧化物-半导体界面处的表面费米能级钉扎问题。

从那时起,InGaAs MOSFET的性能飞速增长。但是,问题仍然存在。制造FinFET需要对沟道侧壁进行激进的等离子刻蚀,而这可能是造成电子传输受损的原因,我们旨在通过热ALE技术解决这个问题。

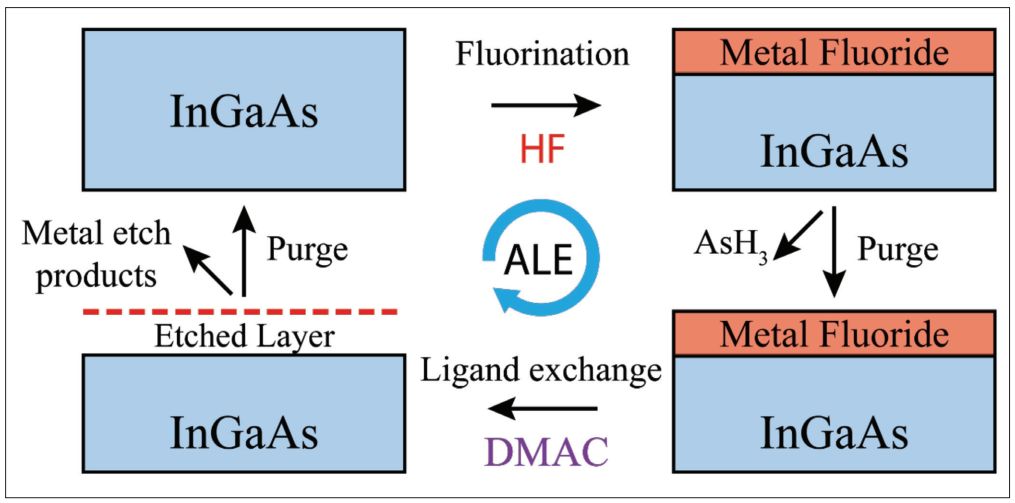

经过一些实验,我们为III-V族材料开发了一种有效的热ALE工艺。前半个循环是使用气态氢氟酸的表面氟化步骤,后半个循环是配体交换过程,去除了表面金属氟化物(具体过程参见图1)。使用二甲基氯化铝去除金属氟化物,刻蚀过程中产生的易挥发性产物也会在300℃高温下除去。如果我们需要增加刻蚀的深度,我们只需重复该循环即可。

图1. InGaAs热原子层刻蚀的完整循环示意图。在第一个半周期中,对InGaAs表面进行氟化处理,并形成金属氟化物。在第二个半循环中,通过配位体交换过程去除了金属氟化物。 每个半周期内形成的挥发性刻蚀产物都会被除去。

在300℃的试验中,对于InGaAs和InAlAs,刻蚀速率分别确定为0.2Å/循环和0.6Å/循环。相比之下,常规的自限制刻蚀方法例如数字刻蚀通常以1 nm /周期的速率刻蚀,这表明InGaAs热ALE慢了大约50倍。这不是劣势而是优势,因为当这项技术用于深纳米级器件制造时,它可提供前所未有的刻蚀控制和精度。

更令人兴奋的是,ALE和ALD存在工艺相似性使得能够在同一反应器中实现这两种工艺。这样使我们可以实施原位ALE-ALD复合工艺,是在FinFET中形成MOS栅极叠层的理想工艺。我们使用以无等离子体、各向同性方式热ALE工艺完成刻蚀鳍片侧壁,然后采用ALD工艺沉积栅极电介质和金属材料进行覆盖。

这种方法大有前景。它完全可以防止MOS界面暴露于空气中,并且工艺十分灵活。决定将化学前体引入反应器之后,可以在刻蚀和沉积之间自由切换。借助这些优势以及制程高可控性,该工艺提供了纳米级器件制造的新方法,有助于显着提高晶体管性能。

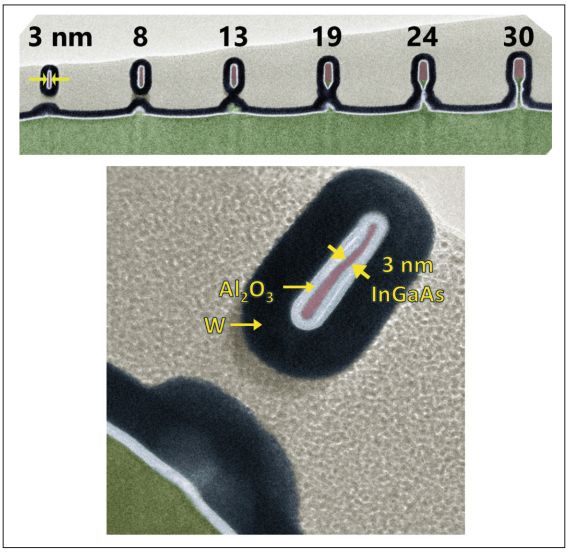

图2. 通过ALE-ALD复合工艺制造的(顶部)InGaAs鳍片(鳍宽度为3 nm至30 nm)和(底部)最小的被隔断的InGaAs鳍片(横截面为3 nm)的横截面透射电子显微镜图像

为了显示ALE-ALD复合工艺的优势,我们使用了这种技术来制造了一系列InGaAs-Al2O3-W环绕式栅极鳍式结构。这些器件均采用原位ALE-ALD复合工艺形成,其InGaAs鳍片的宽度范围从30 nm到仅3 nm(见图2)。我们发现,当鳍片宽度小于20 nm时,由于InGaAs和InAlAs之间的ALE选择性,InGaAs沟道被完全悬置。同时,原位复合工艺还在InGaAs和Al2O3层之间形成了非常清晰的界面,这让我们通过热ALE创制第一个晶体管充满巨大的期望。

小型化FinFET

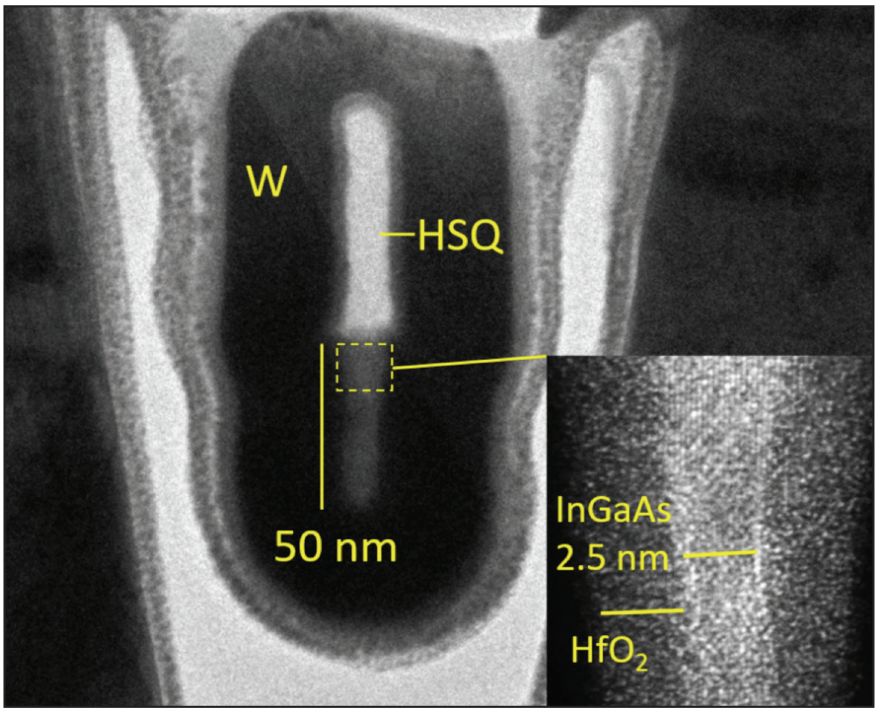

使用原位热ALE-ALD复合技术,我们制造了一系列InGaAs FinFET,鳍片高度为50 nm、宽度为18 nm至2.5 nm(图3为这些晶体管透射电子显微镜剖面)。制造这些极度缩小的III-V FinFET器件的关键在于热ALE极低的刻蚀速率。请注意,FinFET具有HSQ硬掩模,该掩模用于鳍式反应离子刻蚀,并保留在成品晶体管中,以及一个由3 nm的HfO2和30 nm的钨组成的叠层栅极。最小栅极长度为60 nm。

图3. 鳍片宽度为2.5 nm,长度为50nm的InGaAs FinFET的横截面透射电子显微镜图像。(鳍片上部的特写照片。)

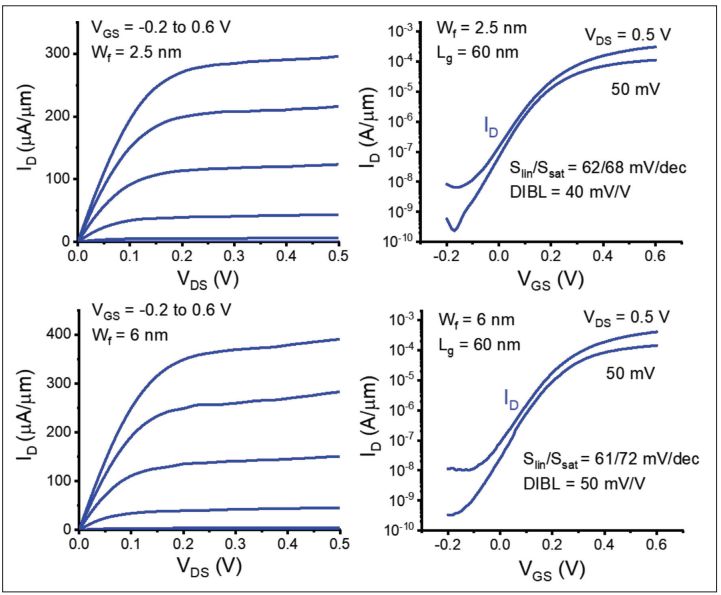

ALE工艺的优点不仅在于制造极小的器件,还在于性能上的显着提高,这是由于关键氧化物半导体界面没有暴露于空气,它常出现在制造工艺中。在我们的InGaAs FinFET上进行的测量表明,即使对于2.5 nm宽的鳍片(见图4),晶体管的性能也很好。对于这些晶体管,在线性和饱和区域下,亚阈值斜率分别仅为60和62 mV /decade。这些接近理想的数值体现了这些器件快速关断的能力,其源于高质量的MOS界面。

图 4. 通过原位热ALE-ALD工艺制造的InGaAs FinFET的输出和亚阈值特性。

FinFET的栅极长度为60 nm,鳍片宽度为2.5 nm(顶行)和6 nm(底行)。

所有品质因数均通过导电栅极外围进行归一化。

我们发现,鳍片宽度的差异会导致跨导最大值的变化,这是晶体管导通行为的一种度量。在0.5 V的漏源电压下,对于2.5 nm鳍片最大跨导为0.85 mS /μm,而对于6 nm鳍片的器件最大跨导增加到1.2 mS /μm——后者表现出色的静电性能。对于所有器件,截止状态电流受栅极泄漏的限制。

为了评估该工艺的优势,我们将所制造的FinFET与上一代InGaAs FinFET的特性参数进行了比较。两组晶体管具有相同的器件设计,除了新的热ALE工艺外,它们的制造方式也相同。

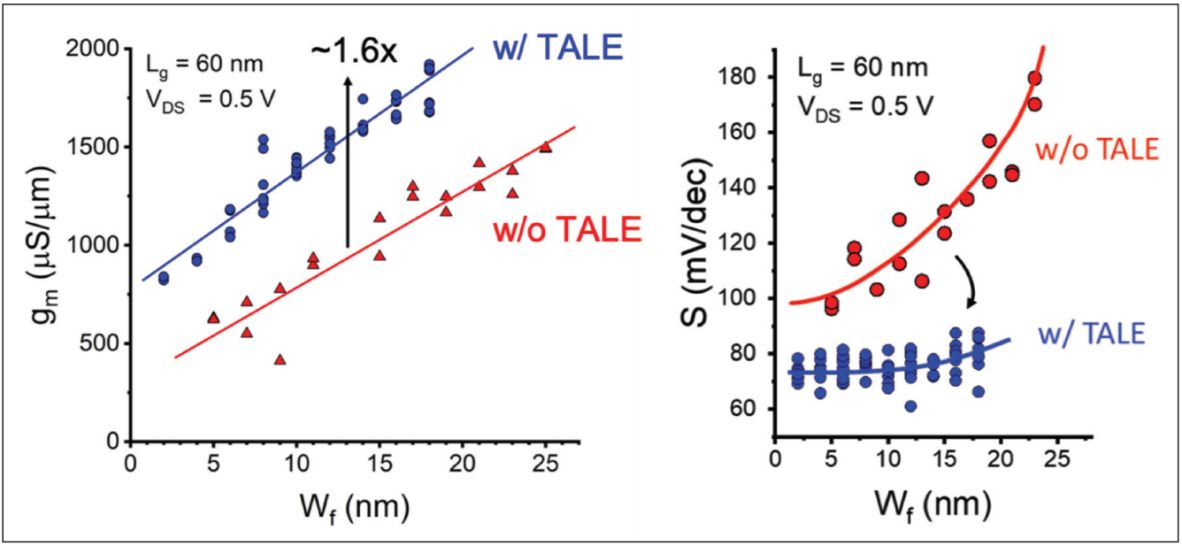

绘制最大跨导和亚阈值斜率为关于鳍片宽度的函数,发现两种类型的FinFET具有相似的变化规律(见图5)。此外,还表明热ALE工艺可以使跨导整体提高60%,并降低了饱和亚阈值斜率。对于新型InGaAs FinFET,线性和饱和状态下的平均亚阈值斜率分别为70和74 mV / dec。相比之下,上一代器件的亚阈值斜率,在鳍片宽度为5 nm时略低于100 mV,而在25 nm时则几乎是5 nm时的两倍。在采用ALE-ALD复合工艺制造的器件中,随着鳍片宽度的增大亚阈值斜率变化很小。

我们还观察到采用ALE / ALD工艺的漏致势垒降低效应持续减少,包括势垒的降低。这一发现以及最大跨导值和亚阈值斜率值,体现了静电控制的极大增强,因为热ALE-ALD工艺获得了高质量的MOS界面。

为了评估最新的InGaAs FinFET的性能,我们已经将它们的峰值跨导与其他最新的InGaAs FinFET进行对标。文献评述显示,在鳍宽度小于20 nm,我们制造的III-V族 FinFET的峰值跨导都达到了创纪录的水平。

我们还将我们的器件与商用硅FinFET进行了比较。对于7 nm鳍片宽度,对应于14 nm和10 nm节点,我们的InGaAs FinFET与英特尔的14 nm节点FinFET的性能相当。考虑到我们的器件具有较低工作电压——InGaAs的VDD为0.5 V,而硅为0.7 V——以及更长的栅极长度,这是一个了不起的结果。

图 5. 在有和没有热ALE-ALD工艺的情况下,VDS = 0.5 V时InGaAs FinFET的跨导(左)和亚阈值斜率(右)与鳍片宽度的关系图。所有FinFET的栅极长度均为60 nm。

鉴于是首次使用热ALE工艺制造晶体管,结果是很令人鼓舞的。它们令人期待,同时强调了热ALE工艺可用于改进其他纳米电子器件的潜力。这项技术的用途非常广泛:可以应用于很多材料和器件结构,例如垂直纳米线;同时,这项技术为工程师提供新机会设计和制造原子级器件。正如费曼所说的:“底部有足够的空间!(There’s plenty of room at the bottom!)”

扩展阅读

1. W. Lu et al. “First Transistor Demonstration of Thermal Atomic Layer Etching: InGaAs FinFETswith sub-5 nm Fin-width Featuring in situ ALEALD”, IEEE IEDM, 2018.

2. K. J. Kanarik ACS J. Phys. Chem. Lett. 9 481(2018)

3. J. A. del Alamo Nature 479 317 (2011)

| 上一篇:222nm的UVC光可灭冠状病... | 下一篇:Micro-LED与量子点显示... |