集成逻辑电路和无线功能

2019/9/23 11:05:58 材料来源:

为硅提供InGaAs沟道,改善了RF-CMOS的逻辑和高频性能。

作者:Cezar Zota, Clarissa Convertino, lukas Czornomaz, IBM苏黎世分部

数字革命定义了我们的时代。我们生活的信息时代是通过大量数据流得以实现,这些数据流通过海底通信电缆传输,通过高频电磁波编码,流入和流出计算机进行处理,现在的计算机借助数十亿个晶体管实现处理功能。今天,我们不仅理所当然地认为我们可以立即获得信息和社交网络,而且还可以持续改进所有这些技术。我们希望智能手机,笔记本电脑和个人电脑变得更快,更高效,并且能够以更高的速率实现连接。

根据Robert Dennard的扩展规律(登纳德缩放比例定律),多年以来,计算机和小工具的发展与硅CMOS的小型化技术保持同步。这些规则确立了一种使硅晶体管小型化的方法,同时改善其性能并保持了芯片的功率密度。这是通过同时降低电源电压和关键晶体管的尺寸(例如栅极氧化物厚度和栅极长度)来实现的。

从20世纪60年代开始,Dennard扩展定律一直到本世纪初都持续运转很好。但最终,电子传输的物理极限已经追赶上了扩展速度,这是通过两个关键现象来单纯地阻止了现代晶体管的进一步缩小。

第一个是电源电压的降低,这可能是自相矛盾的,当导通电流保持在恒定电平时,电压降低将导致关断电流的增加,从而避免处理器时钟速率的降低。实际上,电源电压不能低于0.7V,这是目前最先进的硅CMOS finFET的值。

第二个现象是由于器件进入所谓的“准弹道机制”,这是一种载流子传输模式,电子在通过晶体管沟道时不会散射,由于这种机制将导致随着栅极长度缩小,导通电流的增加会减小。

这两种效应都对进一步缩小尺寸产生显著的影响。这将导致处理器时钟频率不在继续增加,该频率已经在3GHz左右徘徊了十多年。替代方案是,自2003年以来,晶体管尺寸的减小成为更高晶体管密度的关键,并使得多核处理器架构得以引入。

传统缩小尺寸范式失效的另一个影响,是预示了创新和材料科学驱动的发展时代。最近,新技术节点的推出已经不再是尺寸的减小,而是新器件概念和材料的引入。它们包括高κ电介质,应变硅和SiGe,以及finFET器件架构。

III-V族材料能力

这个时期,人们对 材料产生了浓厚的兴趣。它们的高电子迁移率有望改善 CMOS技术中的nFET沟道,并在未来节点中提升驱动电流。例如,InGaAs的电子迁移率是体硅的六倍,并且可以将电源电压降低到0.5V。这是一个很大的进步,因为它会使功耗减半。

已经有持久影响的应用包括高频技术,如雷达和无线通信。HEMT和HBT的改进,在无线技术从20世纪80年代完全模拟的1G格式演变到今天的4G网络中,发挥了重要作用。而且,III-V族材料将成为推出5G的重要原材料,它可以实现10Gbit/s的峰值数据速率,并大大提高网络容量。

工程师已经开发出高频晶体管技术,但是他们遵循与先进硅CMOS并不相同的规则。对于初学者来说,缩小尺寸并不是那么重要。另一个关键区别是该器件采用半导体栅极势垒,而不是氧化物。这种改变使得实现了更高的电子迁移率。然而,这是以降低的静电效率为代价的,因为其结合了相对小的介电常数和栅极泄漏的增加,这源于势垒材料小得多的带隙。这样做的结果就是尺寸缩小会比较有限。取而代之的是,其发展取决于器件结构优化,以及寄生电容和电阻的减小,特别是栅极电阻。

对于III-V族高频晶体管,两个关键性能指标是截止频率ft和最大振荡频率fmax,它们分别是实现电流增益和功率增益的最大频率。自上世纪中叶以来,这两个值都稳步提升,但近十年以来,它们停滞不前,其中ft卡在650GHz左右,fmax也不超过1200GHz。

这有两个原因,都与半导体栅极势垒有关。首先,由于静电控制不足,栅长缩小就没有很好的效率。其次,栅极势垒的厚度不能缩小。如果这样做的话,就会增加栅极的泄漏,因此增加氧化物电容也无法实现。这限制了峰值跨导,从而直接影响ft和fmax。

这两个问题的解决方案是用高k的栅极氧化物代替半导体栅极势垒。在过去的十年中,人们已经进行了很多这方面的努力,专注于高频III-V族MOSFET的演示。迄今为止,它们仍比HEMT在ft和fmax方面滞后大约2倍,这主要是由于栅极氧化物中缺陷的电子散射引起了迁移率的降低。然而,由于尺寸缩小性能方面的改善,MOSFET在跨导方面要优于HEMT。特别是,麻省理工学院的MOSFET显示出巨大的前景,跨导达到3.45mS/mm。这些器件的潜力可以通过在高频兼容架构中实现来获得释放。

更高的频率

高频MOSFET当然不是什么新概念。在硅CMOS工业中,有一类称为RF-CMOS的技术。其基本前提是利用最先进的硅CMOS技术节点,使器件可以同时满足高频和逻辑应用的需求。

这种双重功能有许多优点。它的成本低于III-V族HEMT技术,后者需要III-V族衬底和昂贵的晶体生长方法。此外,通过结合RF电路和逻辑电路,该技术可以实现无线通信功能和数字信号处理等系统的紧密集成。由于这一原因,可以实现延迟和外形尺寸的同步减小,这对于当今的移动通信行业是极其有价值的。

然而,硅技术仍然受到硅这种材料低迁移率的阻碍。例如,英特尔的22纳米RF-CMOS finFET低功耗技术的ft和fmax极限分别仅为230GHz和284GHz。

鉴于此限制,将III-V与RF CMOS技术集成就有很大的吸引力。虽然InGaAs提供的驱动电流在5nm及以下长度范围内对CMOS的提升可能无法完全弥补III-V族沟道的集成成本,但RF性能的大幅提升可能会使III-V族的集成在缩小尺寸时更有优势。

将III-V族与RF CMOS结合起来并不容易。其中面临的挑战包括如何制造具有硅CMOS兼容工艺流程的高性能III-V晶体管,该工艺流程应该尽可能接近标准制造技术,以及如何在硅衬底上集成III-V族沟道的关键问题。此外,还需要在同一种技术中共同优化逻辑电路和高频器件。

在IBM苏黎世分部,我们最近通过努力成功取得了新的突破。我们的方法是通过直接晶圆键合在硅上集成InGaAs沟道。我们在目标硅晶圆和包含沟道的源III-V族晶圆上方覆盖键合氧化物,从而提供键合力。将两个晶圆放到一起,并退火,随后将源晶圆剥离,从而在硅上氧化物层上留下III-V族薄层。

过去十年中,直接晶圆键合技术已经突飞猛进。它现在是III-V族集成的主要候选方式,因为它解决了几个关键挑战。包括它能够进行大面积晶圆键合,昂贵的III-V族衬底可重复使用,与预处理晶圆的键合,以及与适合n FET和p FET沟道层的集成。

改进的空间仍然存在,因为需要降低键合缺陷密度以确保III-V族材料层的高迁移率。然而,毫无疑问的是,直接晶圆键合已经成熟为马上可以进入工业用途的技术。

我们的III-V族RF-CMOS技术的优势之一是它采用硅CMOS完全兼容的工艺流程。工艺包括首先栅极高κ/金属栅极流程,形成凸起和原位掺杂的自对准源极和漏极区域,同时使用硅兼容的材料。通过采用这种方法,我们凸显出硅技术中经济高效地引入III-V族材料的可能性。额外的代工成本得以最小化。

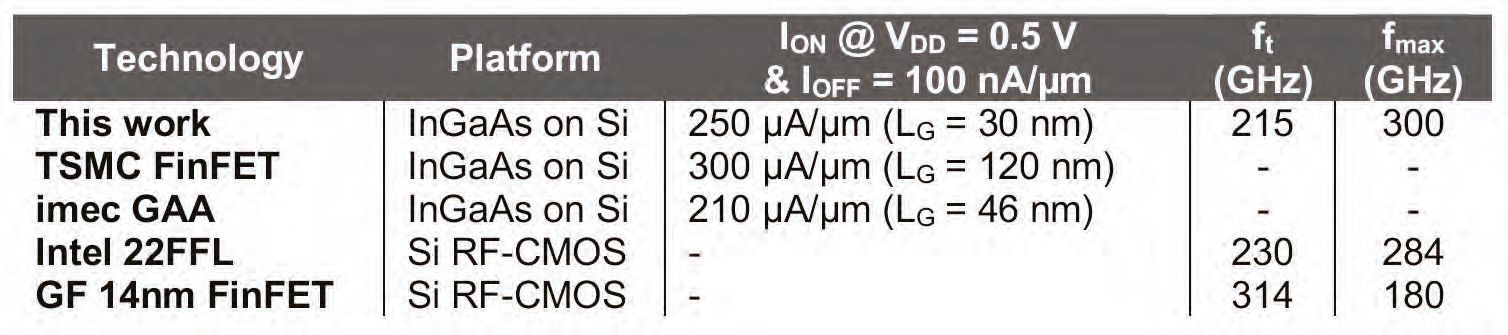

我们已经使用我们的工艺技术制造了具有20nm宽InGaAs鳍的finFET。在具有可比尺寸栅极长度上,针对硅上III-V族进行了基准测试,结果显示我们最新的晶体管与最先进的晶体管可相媲美,这里也包括我们在2017年IEDM上报告的与我们仅针对逻辑电路的平台进行比较。该评估基于250μA/μm的驱动电流,实现了固定的关断电流和0.5V的电源电压。

我们最新的芯片还具有RF-MOSFET。该芯片同时提供令人印象深刻的高频和逻辑性能,这是通过SiN源极和漏极隔离实现的,这些隔离减少了与栅极电极,以及隔离下方源极和漏极接触扩展的重叠电容。注意,简单地添加隔离以减小寄生电容,并希望藉此改善高频性能并不够好,因为这通过在隔离下方沟道的非栅极部分中引入大的接入电阻,从而会降低逻辑性能。我们采用一种新颖的方法来避免这种情况,该方法包括在隔离下方一个小空腔的可控蚀刻,然后再填充低电阻的接触材料,从而减少对接入电阻的影响。

采用这种架构,我们的InGaAs RF-MOSFET能够达到400GHz的ft,这是迄今为止报告的III-V族RF-MOSFET最高值。随着我们器件布局的优化,我们获得了ft为215GHz和fmax为300GHz的平衡性能。这些值接近英特尔和格罗方德的硅RF-CMOS性能。

更高的频率是可能的。电容仍然是高频性能的限制,因而可以通过更厚的隔离和更长的接触扩展来实施改进。另一个优化是在沟道中引入薄量子阱。这将通过减少栅极和背面氧化物界面处的散射,实现迁移率的增加。通过这些改变,应该能够推动我们的技术从与最先进的硅等效产品性能相匹配,达到以相当大的优势超越它们,并最终成为III-V族和硅集成的强有力实例。

作者注:本工作得到Horizon 2020支持协议的资助,资助号688784(INSIGHT)。

集成逻辑电路与无线功能其中所面临的挑战包括:如何制造具有硅CMOS兼容工艺流程的高性能III-V晶体管,该工艺流程应该尽可能接近标准制造技术,以及如何在硅衬底上集成III-V族沟道的关键问题。

扩展阅读

H. Hahn et al. IEDM Tech. Dig. 17.5.1-17.5.4 (2017)

B. Sell et al. IEDM Tech. Dig. 685 (2017)

C. Zota et al. VLSI Techn. Symp. T15-5 (2018)

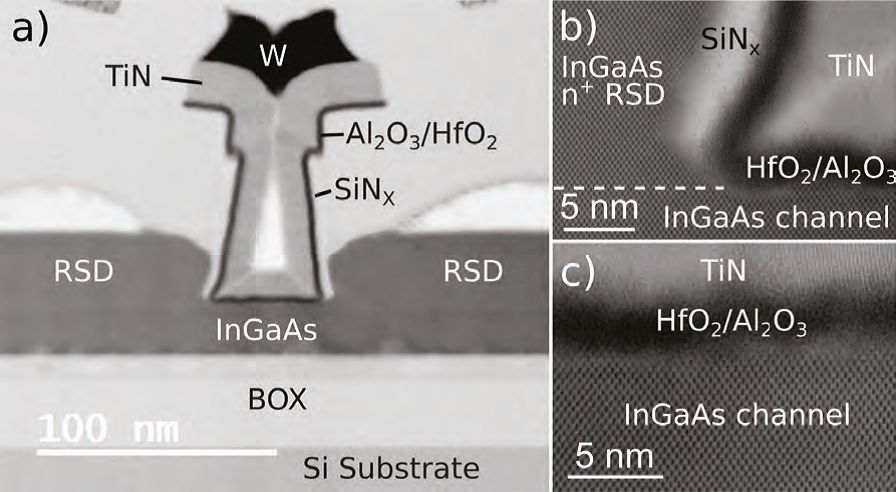

图1. (a)所制造的RF-MOSFET横截面透射电子显微镜图。(b)接触侧特写,显示出凸起的接触外延以及SiN隔离,这通过将接触与栅极分离从而减小了寄生电容。(c)沟道区和栅极氧化物界面特写,接近显示出III-V族材料的原始晶体质量。

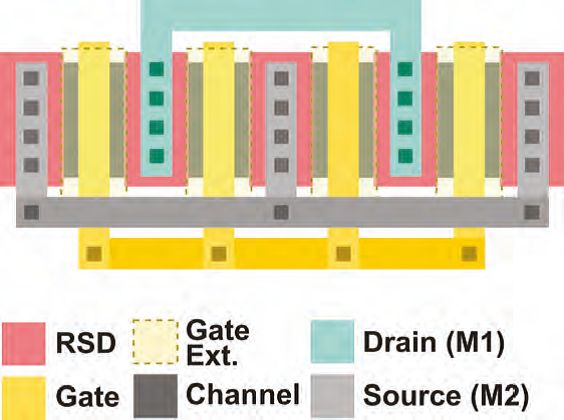

图2. 具有四个栅极叉指的IBM RF-MOSFET的布局图。栅极延伸层显示为栅极金属顶部上的额外金属线,用于降低栅极电阻。

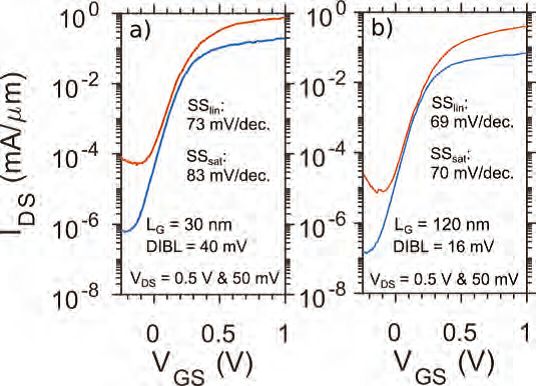

图3. 逻辑应用中短沟道和长沟道finFET的亚阈值特性图。finFET的三栅极结构改善了静电控制,从而减少了预期偏置点处的截止电流。

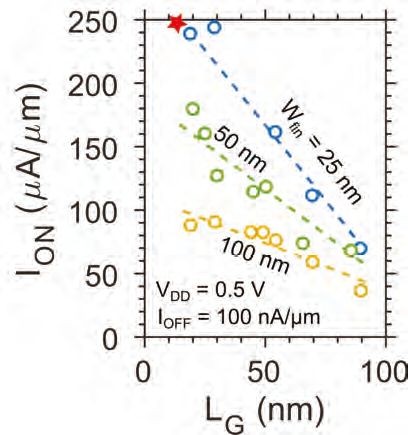

图4. 各种栅极长度时,针对在特定电源偏置和关断电流下定义的导通电流的比较图。红色星形表示的时IBM在2017年IEDM会议上之前的结果,这是一种单纯适用于逻辑电路的技术。借助IBM的最新技术,可以实现类似的逻辑性能,同时还能够实现高频功能。

表1. 各种硅上III-V族技术以及最先进硅RF-CMOS的基准数据。通过比较高频性能,我们的新工作首次展示了出III-V族可以与硅RF-CMOS相匹配的性能。

| 上一篇:镁掺杂效率随 GaN 的平... | 下一篇:欧司朗“先进之光”点亮... |