中科院微电子所在高密度低应力硅通孔(TSV)研究方面取得新进展

材料来源:中国科学院微电子研究所

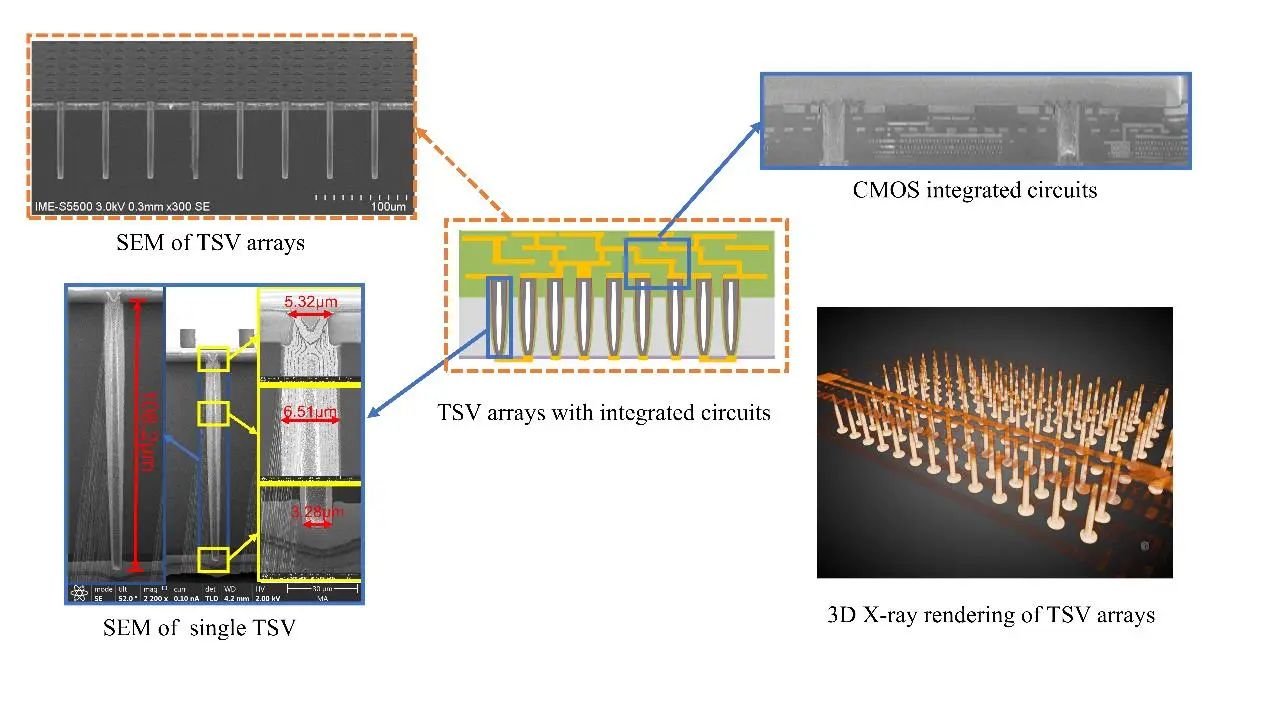

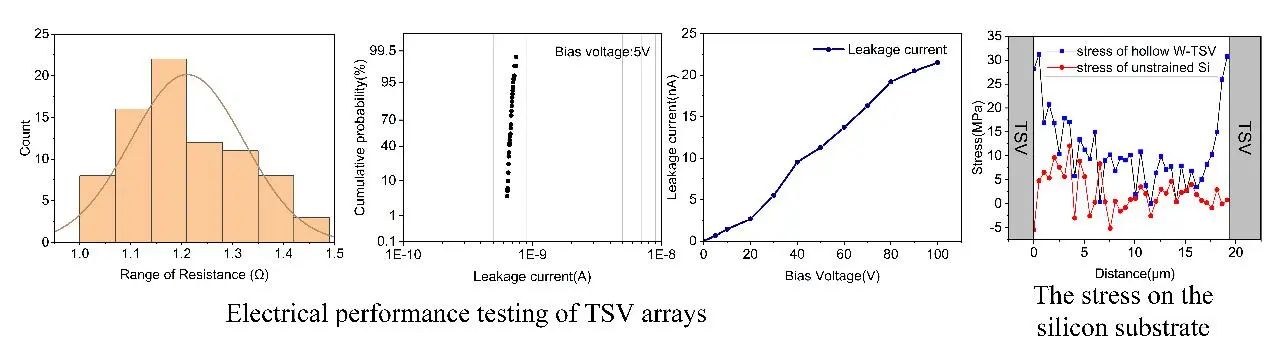

三维(3D)集成技术是制造低功耗、高性能和高集成密度器件的必备技术,有望突破摩尔定律限制。TSV作为3D集成的核心技术,具有缩短互连路径和减小封装尺寸的优势。目前,高密度TSV互连在近传感器和传感器内计算、混合存储立方体、高带宽存储器(HBM)、互补金属氧化物半导体(CMOS)图像传感器、制冷和非制冷焦平面阵列、有源像素传感器等具有重要应用前景。但在高密度应用场景下,由于硅衬底与TSV互连金属之间热膨胀系数不匹配,TSV存在严重的热应力问题,会导致晶体管迁移率和参数偏移进而影响器件性能,甚至导致器件损坏,亟需通过结构调控抑制热应力对器件可靠性的影响。

基于该成果的论文“Low-Stress TSV Arrays for High-Density Interconnection”近期发表在中国工程院院刊Engineering(2095-8099,2095-8099,https://doi.org/10.1016/j.eng.2023.11.023)。微电子所焦斌斌研究员为论文第一作者兼通讯作者,乔靖评博士为论文第二作者。该研究成果同时被2023 IEEE 73rd Electronic Components and Technology Conference (ECTC)会议收录,并以分会场报告的形式展示。

论文链接:https://www.sciencedirect.com/science/article/pii/S209580992400153X

高密度互连的低应力TSV设计与制备

高密度互连的低应力TSV设计与制备

| 上一篇:台积电计划 2025 年推出... | 下一篇:垂直GaN功率器件公司Od... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk