企业新闻详细内容

CEA-Leti开发出兼容CMOS的200 mm GaN-on-Si工艺

材料来源:雅时

CEA-Leti已开发出一种与CMOS洁净室兼容的200 mm GaN/Si工艺技术,这项技术既能保持半导体材料的高性能,成本又低于现有的GaN/SiC技术。

CEA-Leti已开发出一种与CMOS洁净室兼容的200 mm GaN/Si工艺技术,这项技术既能保持半导体材料的高性能,成本又低于现有的GaN/SiC技术。

IEDM 2023共有九场演讲,该研究所在其中一场演讲中表示,目前用于电信或雷达的GaN高电子迁移率晶体管(HEMT)技术采用的是小型GaN/SiC衬底,需要在专用洁净室中加工。

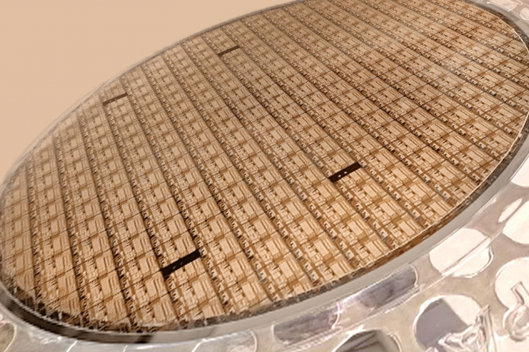

用于生长GaN层的高性能SiC衬底非常昂贵,而且只有相对较小的尺寸。而该研发项目在兼容CMOS的洁净室中相继开发了直径为200 mm和300 mm的GaN/Si晶圆,以降低衬底成本,并充分利用现有的高性能洁净室设施。

因此,在功率密度方面,CEA-Leti的GaN/Si技术在28 GHz的性能正逐步超越GaN/SiC技术。

CEA-Leti科学家兼论文“兼容CMOS且带有原位SiN栅极电介质和低温欧姆触点的6.6W/mm 200 mm AlN/GaN/Si MIS-HEMT”主要作者Erwan Morvan表示:“我们的目标是通过兼容CMOS的200 mm GaN/Si技术,在约30 GHz频率下达到目前最先进的GaN HEMT性能,并与GaN/SiC技术竞争。”

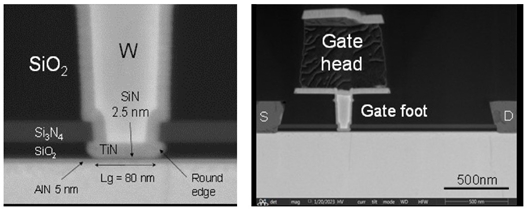

AlN/GaN MIS-HEMT的扫描透射电子显微镜横截面及栅脚放大图

AlN/GaN MIS-HEMT的扫描透射电子显微镜横截面及栅脚放大图

Erwan Morvan还表示:“这项研究表明,兼容CMOS的200 mm硅基SiN/AlN/GaN MIS-HEMT技术在5G/6G基础设施、卫星通信、无人机探测雷达或地球观测等应用中大有可为。该技术在保持高功率密度、高效率、轻质、紧凑的同时,还能降低器件成本。”

此研究中开发的器件专为射频放大器和开关而设计,可用于30 GHz左右的这些应用。

虽然这项工艺技术的可靠性测试才刚刚开始,但CEA-Leti将持续在该领域进行研发工作,包括提高其MIS-HEMT晶体管的原始输出功率和效率,集成其改进的工艺模块以提高器件性能并将工作频率提高到100 GHz以上,以及在300mm硅晶片上实现GaN/Si芯片的三维集成。

【近期会议】

2024年1月11日14:00,雅时国际商讯联合汉高中国粘合剂电子事业部即将举办“未来功率半导体的封装趋势和挑战”专题会议,推动功率半导体封装产业的协同发展和生态创新!诚邀您上线参会交流互动:https://w.lwc.cn/s/2iMvi2

| 上一篇:中科院宁波材料所研发新... | 下一篇:卡迪夫大学与IQE延长合... |

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:lynnw@actintl.com.hk